kicad-design-for-manufacture

2017-02-02 Robin Whittle

rw@firstpr.com.au This page concerns various questions of how to design PCBs in general, and with KiCad in particular, so that they both work and can be manufactured reliably and efficiently. I am not an expert in these matters. I initially wrote it in late October to mid-December 2017, while doing my first KiCad design, which was also my first SMT PCB.

(2023-09-02 mini update: I am not sure how relevant all this material is to Kicad in 2023. I haven't done any work with it since 2018. Today I updated a link to Andrew Tweddle's site, which is now https://pcbsynergy.com .)

One subject I consider is how to design footprints to match accepted standards regarding the centroid and zero rotation, and to meet other requirements, so that there is minimal need for manual effort, and minimal chances of errors, when using the .pos files (centroid files) produced by KiCad, to drive (via various other software used by the PCB assembly company) pick and place machines, for automated SMT assembly. I am not specifically considering automated through hole assembly, and I am only thinking about SMT on a single side for now.

Another perplexing problem I tried to solve (so far, I think, with success) is how to define the pads so they will work reliably with reflow soldering, while also being suitable for hand soldering for assembly, modification and repair.

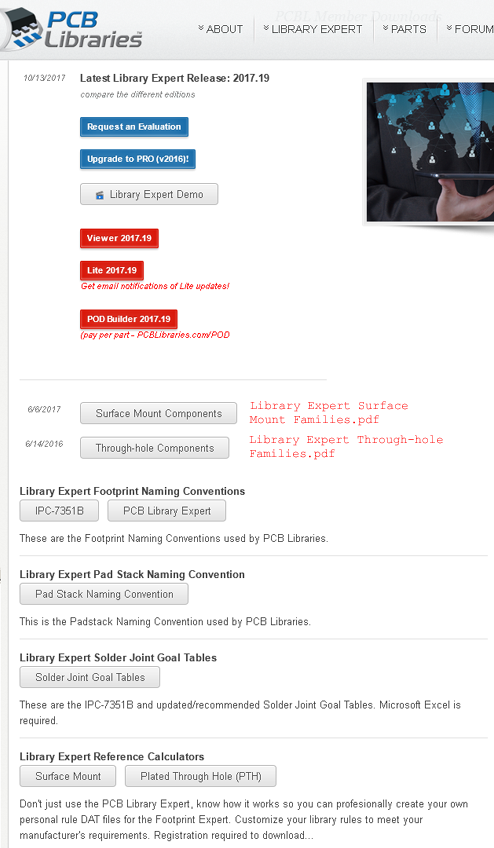

I describe, in several sections below, how I made SMT footprints for my footprint library, primarily by using the freely available Windows program Library Expert LITE from pcblibraries.com, followed by some manual (and potentially automated) editing of the resulting footprint file. The editing achieves some things which differ from what is allowed by the KiCad Library Convention (KLC) approach to footprints, and from what would be achieved if I simply imported into my library (via Footprint Editor) the files exported by Library Expert Lite. (Some of these are based on how Mars_Warrior, writing on the KiCad.info forum, describes his way of designing PCBs.)

- The F.SilkS layer is used, as is conventional, for the reference of the component.

- Instead of using the F.Fab layer for the component outline and value, I use it for the component outline and reference.

- I use the Eco1.User layer to show the component outline and value.

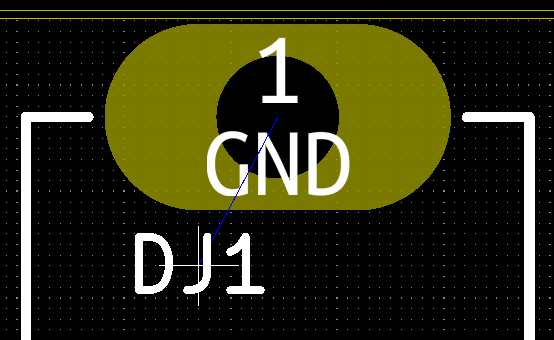

- Library

Expert Lite creates footprints with SMT pads as rounded

rectangles and many other details which are compliant with the

forthcoming IPC-7351C standard. The typically long and detailed

names it creates for footprints are also compliant with that standard

and I frequently use these names - perhaps with some extra characters

for something more easily recognised by mortals -for my footprint

names. This is different from the KLC approach to naming.

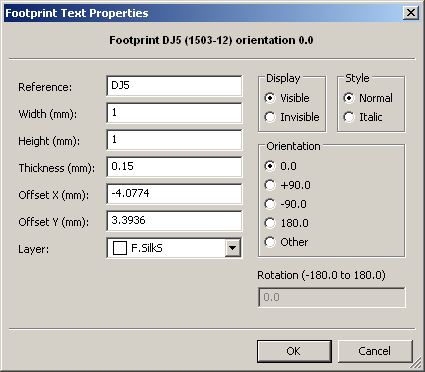

- I change the size and line width of the text on these three

layers so it is all quite small: 0.80mm x 0.80mm with 0.15mm line

width. This is as small as my PCB manufacturer recommends for the

silkscreen layer. For some or many components in the

finished PCB design I will want the final text on F.SilkS and perhaps on F.Fab and Eco1.User

to be bigger than this, with thicker lines. I will change these

sizes manually as I design the circuit board. I would rather

start with small text since it clutters things less than larger text.

- In December 2017, no official release of KiCad supports rounded

rectangle pads, so when Library Expert Lite exports a footprint in

KiCad format, the pads are specified as ordinary rectangles. With

a text editor (or in the future perhaps a program to do the same thing)

it is reasonably easy to alter the footprint file to make all desired

rectangular pads into rounded rectangles, before importing it into

Footprint Editor, which I use to save the footprint to my

library. It is also possible to make these changes manually in

Footprint Editor.

- Although this does not affect footprints, my approach to PCB design involves using the Eco2.User layer

for lines depicting where I want the board edges to be routed

(milled). These lines and text on this layer will be in one of

the Gerber files I send to my PCB manufacturer. I do not use the Edge.Cuts layer since, according to the Pcbnew manual, any text on this layer also appears on other layers.

The final section consists of links and notes on other aspects of designing PCBs to ensure reliable and efficient manufacture of the board itself and the complete assembly of all SMT components.

Please see the parent directory for other pages I have written about how I use KiCad: ../

There may be discussion of this page on the Kicad.Info forum:

Contents

| #footprints |

01 -

Footprint centroids and zero rotation, including how to make KiCad

footprints to IPC-7351 standards manually, with Footprint Editor,

without using a standards document, and also how to make them with the

freely available Library Expert Lite, export them to KiCad and fix them

up a little before placing them in a library |

| #footprintnames |

02 - Systematic approaches to naming footprints, based on IPC-7351C |

| #initzerorotation | 03 - Initial zero rotation for SMT components: IPC-7351C Level A or B? |

| #schemsymb | 04 - Schematic symbol names |

| #validating | 05 - Validating and fine-tuning the BoM and .pos (centroid) files against the Gerber and drill files, including with VisualPlace |

| #footprintnotes |

06 - Some notes on making my own footprints |

| #pcbdfm | 07 - Various web pages, forum discussions and documents regarding PCB design for manufacture |

Some notes written on 2018-01-02, a few weeks after I wrote most of this page:

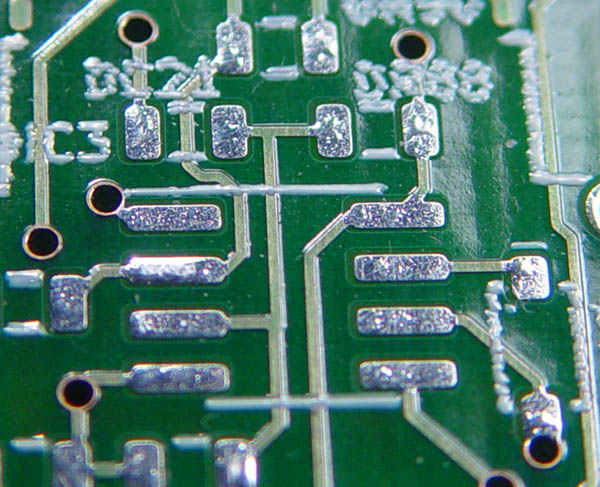

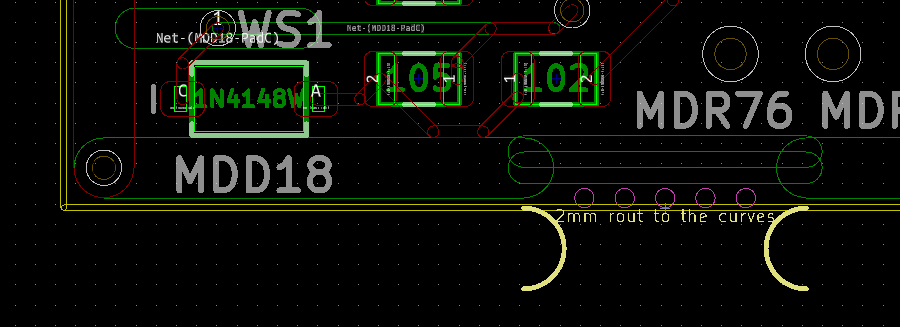

I now have some prototypes made by PCBFast

here in Australia - in Seaford, south-east of Melbourne. The boards arrived a week after I emailed them the

Gerber and drill files. The inkjet legend ("silkscreen") is a little

ragged, but that's fine. The boards were perfect in every other

respect.

Although I haven't tried automatic placement and reflow soldering of these boards, I have hand-assembled some of them. There are various mistakes, but the footprints themselves, all of which were generated as described below by adapting the exported files of Library Expert, all look good. I used a late November Windows nightly of KiCad, which supports rounded rectangle pads, which the current release doesn't. KiCad version 5 will support rounded rectangle pads.

Thanks to the KiCad developers and PCBLibraries.com for the tools which enabled my first surface mount PCB design to be, as far as I know, a complete success (except for my own mistakes)!

Although I haven't tried automatic placement and reflow soldering of these boards, I have hand-assembled some of them. There are various mistakes, but the footprints themselves, all of which were generated as described below by adapting the exported files of Library Expert, all look good. I used a late November Windows nightly of KiCad, which supports rounded rectangle pads, which the current release doesn't. KiCad version 5 will support rounded rectangle pads.

Thanks to the KiCad developers and PCBLibraries.com for the tools which enabled my first surface mount PCB design to be, as far as I know, a complete success (except for my own mistakes)!

The via at the end of the diode's pad (lower right) is my mistake. The soldermask clearance (Dimensions > Pad to mask clearance > Soldermask clearance) was set to 0.125mm, according to PCBFast's recommendation, but my impression is that this value should be reduced. Note the weedy little little polarity line of the diode on the right, which is barely visible at the edge of the solder resist.

The main text of this web page has not been updated to reflect everything I know now that I have the physical boards. Nor have my libraries, which you can grab here and use as you wish:

Some things I learned were:

- The polarity line on the diodes needs to be at least twice as

thick, and moved away from the pad a little. In these prototype PCBs

the line was a single set of inkjet dots, and these sometimes fell

partially into the area lacking soldermask, which meant they did not

exist at all on these boards. Also, the errors inherent in the inkjet

process scattered the dots from the straight row they should be, so a

thicker line, hopefully producing a line two dots wide, would be better.

Hopefully the production boards, which are made in China, will use actual silkscreen for the white legend, but I have not confirmed this. (PCBFast is one of the two remaining PCB manufacturers in Australia. The other is http://www.lintek.com.au in Queanbeyan, NSW. Lintek do beautiful work, including with exotic PTFE microwave materials, and consequently do a lot of jobs for overseas customers. PCBFast used to be a full scale manufacturer, but now they make prototypes and have their quantity production done in China. My experience with PCBFast recently and with the last batch of Devil Fish boards has been 100% positive.)

- When I wrote the material below, I used three digit

numbers for resistor values, such as 223 and 104, thinking that the

actual resistors on the PCB would have these numbers printed on

them. Then I learned three things to my surprise: Firstly,

my SMT resistor book (which had 5% 0805 resistors printed like this)

did not have all the the E12 value range I assumed it had (1.0, 1.2,

1.5, 1.8, 2.2, 2.7, 3.3, 3.9, 4.7, 5.6, 6.8, 7.5, 8.2) - and I couldn't

find any on eBay which did. Secondly, many 0805 resistors from

element14 or Mouser have no markings at all. Thirdly, those which

do have markings are almost always 1% resistors and part of a much

finer range of values than the E12 range, so they have four digit

markings: 2204 and 1003.

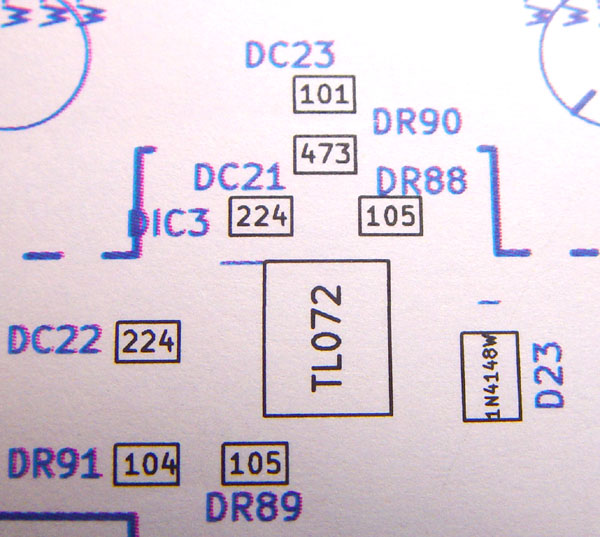

So I will revise schematics to have 4 digit resistor numbers in the PCBValue field and these will appear in the print-out from the ECO1.User layer. (Printed by exporting to SVG and then opening and printing with Inkscape.) This will solve a pesky problem in my current three digit arrangement - capacitors with numbers such as 104 (0.1uF) being visibly indistinguishable on this layer from resistors with a 100k value.

- I should alter the footprints for the smaller SMT components, which have a small square on the ECO1.User layer, to use 0.4;0.4;0.1 text for this layer. This will enable three or four digits to fit inside the square.

This should work well if I have these value text items (mainly from the schematic's PCBValue fields) printed on the same piece of paper as the F.SilkS layer, since those items are outside the outline of the component. This can be done by two separate SVG exports, one for each layer, in black, and then by importing both into Inkscape, one at a time, changing their colours, and placing each layer's set of lines and characters one on top of the other in a third Inkscape document, which can then be printed:

This is with the 3 digit resistor values using text size 0.6; 0.6; 1.2. The diode uses 0.4; 0.4; 0.1. The printer is a 600DPI LED Brother HL-3170CDW. Apart from some colour registration errors, it produces an exceedingly crisp image.

I will likewise reconsider footprint library text sizes for the F.Fab layer, so they could generally fit into the boxes like this, for a separate print-out of references to help the PCB assembly people. For now I haven't worked on the placement or size of the F.Fab layer text.

In what follows I did not consider a significant addition to the various KiCad libraries which are made available by various designers, and programmers who automatically generate such libraries (of footprints at least) - Digi-Key's schematic symbol and PCB footprint library for KiCad:

(This was in November or early

December 2017 - this forum software doesn't seem to have concrete dates

and times for messages. The forum software frustrates my attempts

to treat a discussion as a concrete thing which can be printed.

Messages appear or are hidden according to processes beyond my

understanding.)

I haven't looked at these closely, but this is clearly a great addition to KiCad. On 2017-12-02 I made these text files listing the names of the symbols and footprints:

(The first of these was made with FileLocator Pro, the free version of which is Agent Ransack. These programs have all sorts of uses for searching for text in multiple files, directories of files etc.)

#footprints

01 - Footprint centroids and zero rotation , including how to make KiCad footprints to IPC-7351 standards manually, with Footprint Editor, without using a standards document, and also how to make them with the freely available Library Expert Lite, export them to KiCad and fix them up a little before placing them in a library

I don't have a clear idea how SMT PCB assemblers

program their pick and place machines (but see my notes on VisualPlace and NPI software below), but I want to design all the

footprints in my library so that my PCB

designs and resulting files will be as easy as possible to use for

setting up the automated assembly process.

In order to reduce manual effort and potential problems in the automated SMT assembly process, I need to make the correct choices in these regards for my schematic and footprint libraries, including:

If you think this page is in some way authoritative or a complete solution to the challenges of making footprints, please take a look at well informed people with much more experience than I have discussing this field, such as:

I think found this discussion and document extremely informative and I suggest you read them fully if you are at all interested in KiCad footprint libraries. The discussion is in a forum with characteristics I found annoying . We have to click on links to see all the replies. I found no way of printing the whole thing, and some replies seem to be repeated. Still, I think it is worth reading all the replies and following quite a few of the links.

In addition to the PCB assembly company needing the Gerber files of the whole panel of PCBs, and/or of a single PCB, they will need:

The complete design must also include, for each component (or at least each SMT component) an outline on the front (top) courtyard layer F.Crtyd, since I am only planning on components on the top (AKA front) side. This is needed when manually placing the components in the PCB design so their courtyards do not overlap.

All these things need to be considered when creating footprints for my library. Then, from the industry standard pin numbers/names (3, A, CE or whatever) of these footprints, I can create matching schematic components ("schematic symbols" is also a better term) with pin numbers/names to match these footprints.

KiCad is intended by its designers to support a schematic symbol library which does not normally specify a single footprint for each symbol (though there is a field in each symbol for doing so), but leaves it open, perhaps with some guidance by way of filters, for which footprints will be chosen once the schematic is complete and it is time to create a PCB design. I, and many others, have footprints set in at least some of the schematic library components. I design the schematic in sections, with each section being implemented in the PCB design, rather than leaving the PCB design to a completely separate stage after the schematic is supposedly finished. This process involves revisions to already existing sections of the schematic and PCB design. For instance, the choice of which sub-section of dual and quad op-amps to use, or sections within a multi-gate logic chip, depend on how we lay out the PCB. Likewise the assignment of actual firmware-supported functions to particular pins of a microcontroller may depend on the PCB layout.

A list of file types within KiCad is in the main (small) KiCad manual, section 1.2:

I am not sure if there is a formal specification for the format of the .pos file, or whether the format is specified somewhere outside the KiCad project due to it being some kind of industry standard. It seems that the KiCad .pos file is an instance of a more general concept, which is not specific to KiCad or any other system: a centroid file AKA centroid data. Pick-and-place file, PnP file or P&P file are terms for the same or a similar concept. Googling these terms finds lots of pages, including this file describing a particular assembly company's specification for a centroid file:

The details of such a file, supplied to the assembler, would vary considerably depending on whether it was for a single instance of a finished PCB, or for an entire panel (AKA array) of finished PCBs which is actually manufactured and assembled as a single panel. The centroid file only concerns components which will be automatically placed on the board, so for me this is just the SMT components.

Searching for recent KiCad .pos files on the Web (Printed by Pcbnew version kicad 4.0.7) I found no files, but for 4.0.5, here is an example of a KiCad .pos file. The angles are counter-clockwise and the centroid locations are in millimetres, relative to some reference point, which should be the same as the reference point for the Gerber files (or at least this would be the most convenient arrangement for running VisualPlace).

When my first PCB design is finished, I will check the resulting BoM and .pos files with the awesome free (as in beer, not open-source) Windows program VisualPlace from CompuPhase in the Netherlands:

In order to reduce manual effort and potential problems in the automated SMT assembly process, I need to make the correct choices in these regards for my schematic and footprint libraries, including:

- The naming of pins needs to be the same as is expected by people

and software, based on various accepted standards. For

instance, the numbering of the positive pin of an electrically

polarized electrolytic capacitor - should it be 1, 2 or something else?

It certainly needs to match the numbering of pins (or pads for SMT) in

the corresponding one or more schematic symbols in my library.

- The naming, numbering or whatever of pads/pins in the footprint

library needs to conform as noted above to expectations by people and

software, not least VisualPlace, which I will be using to check my .pos and BoM (Bill of Materials) files.

- When I define a footprint in my library, it has within it an origin or

centroid - wherever in the footprint both X and Y are zero. The

footprint's rotational orientation in the library is important, since

it will be rotated by some angle, perhaps zero, when placed in the

PCB design, and this rotational angle will be output in the .pos file

to be used (after various processes and checks) to tell the

PCB assembly company's pick-and-place machine how to rotate a component it picks up from a

tape (or tray, or tube feeder) before placing it on the PCB.

I need to get the location of this centroid, and the initial orientation (rotation) of the footprint right, which means complying with accepted industry standards - the forthcoming IPC-7351C.

- I also need to design the precise footprint details, the exact

shapes of pads, choices of holes (for through-hole parts) etc. so they

work reliably in terms of reflow soldering (SMT only) and manual soldering (through hole parts).

This involves considerations of the overall density of component

placement in the final PCB, how easy it would be to manually desolder

and resolder components, how easy it would be to use test probes

etc. Fortunately there is guidance on this and I generally choose

to use the guidance for "medium" density, AKA "median" or "normal"

density.

- The names of footprints involve some choices. I could use plain imperial names such as 0805and

not bother with their metric equivalent. This seems to be

what most people do, but I think that using these alone is not the way

to build a library which I will use for the next few decades.

Below I link to documents which lay out an elaborate scheme for naming

footprints. In practice, I use Library Expert Lite's names.

- I want to use footprints with rounded rectangle pads for SMT, so I am using a development version (nightly compilation) of KiCad, rather than the current (October 2017) release version 4.0.7. For some of what follows I used a 2017-09-19 development version. Then I used later ones, such as from 2017-11-01. These are all Windows nightlies: http://downloads.kicad-pcb.org/windows/nightly/

If you think this page is in some way authoritative or a complete solution to the challenges of making footprints, please take a look at well informed people with much more experience than I have discussing this field, such as:

#thread00

https://forum.kicad.info/t/why-are-the-kicad-library-conventions-non-ipc-compliant/3678/

#pcblib2013

http://www.pcblibraries.com/downloads/Guidelines%21PCB_Design_Optimization_Starts_in_the_CAD_Library.asp

https://forum.kicad.info/t/why-are-the-kicad-library-conventions-non-ipc-compliant/3678/

#pcblib2013

http://www.pcblibraries.com/downloads/Guidelines%21PCB_Design_Optimization_Starts_in_the_CAD_Library.asp

I think found this discussion and document extremely informative and I suggest you read them fully if you are at all interested in KiCad footprint libraries. The discussion is in a forum with characteristics I found annoying . We have to click on links to see all the replies. I found no way of printing the whole thing, and some replies seem to be repeated. Still, I think it is worth reading all the replies and following quite a few of the links.

In addition to the PCB assembly company needing the Gerber files of the whole panel of PCBs, and/or of a single PCB, they will need:

- A Bill of Materials (BoM) file. See my notes on other pages here ../ about generating BoM files in various forms.

- The .pos file produced by KiCad, or some derivatives of this file which is more suitable for them.

- A PDF of the F.Fab layer of

the PCB design. At least for the SMT components, this will

contain an outline of each component's package, and within it the

reference designator (C10, R56

etc.)

of each component. They will use this to index into the BoM for

all other details, such as the value, part number, possible part

numbers, specification (so they can decide whether one of their

in-stock components is suitable) etc. They might also want a PDF of a the Eco1.User layer, which has these outlines and the value of each SMT component - and probably most through hole components too.

The complete design must also include, for each component (or at least each SMT component) an outline on the front (top) courtyard layer F.Crtyd, since I am only planning on components on the top (AKA front) side. This is needed when manually placing the components in the PCB design so their courtyards do not overlap.

All these things need to be considered when creating footprints for my library. Then, from the industry standard pin numbers/names (3, A, CE or whatever) of these footprints, I can create matching schematic components ("schematic symbols" is also a better term) with pin numbers/names to match these footprints.

KiCad is intended by its designers to support a schematic symbol library which does not normally specify a single footprint for each symbol (though there is a field in each symbol for doing so), but leaves it open, perhaps with some guidance by way of filters, for which footprints will be chosen once the schematic is complete and it is time to create a PCB design. I, and many others, have footprints set in at least some of the schematic library components. I design the schematic in sections, with each section being implemented in the PCB design, rather than leaving the PCB design to a completely separate stage after the schematic is supposedly finished. This process involves revisions to already existing sections of the schematic and PCB design. For instance, the choice of which sub-section of dual and quad op-amps to use, or sections within a multi-gate logic chip, depend on how we lay out the PCB. Likewise the assignment of actual firmware-supported functions to particular pins of a microcontroller may depend on the PCB layout.

A list of file types within KiCad is in the main (small) KiCad manual, section 1.2:

I am not sure if there is a formal specification for the format of the .pos file, or whether the format is specified somewhere outside the KiCad project due to it being some kind of industry standard. It seems that the KiCad .pos file is an instance of a more general concept, which is not specific to KiCad or any other system: a centroid file AKA centroid data. Pick-and-place file, PnP file or P&P file are terms for the same or a similar concept. Googling these terms finds lots of pages, including this file describing a particular assembly company's specification for a centroid file:

The details of such a file, supplied to the assembler, would vary considerably depending on whether it was for a single instance of a finished PCB, or for an entire panel (AKA array) of finished PCBs which is actually manufactured and assembled as a single panel. The centroid file only concerns components which will be automatically placed on the board, so for me this is just the SMT components.

Searching for recent KiCad .pos files on the Web (Printed by Pcbnew version kicad 4.0.7) I found no files, but for 4.0.5, here is an example of a KiCad .pos file. The angles are counter-clockwise and the centroid locations are in millimetres, relative to some reference point, which should be the same as the reference point for the Gerber files (or at least this would be the most convenient arrangement for running VisualPlace).

### Module positions - created on 04/10/17 16:52:49 ###

### Printed by Pcbnew version kicad 4.0.5

## Unit = mm, Angle = deg.

## Side : top

# Ref Val Package PosX PosY Rot Side

C1 1u C_0603 122.5000 -90.5000 90.0000 top

C2 10n C_0603 124.6505 -86.0425 270.0000 top

C3 1u C_0603 127.3500 -98.7500 90.0000 top

C4 47u C_1210 121.0000 -81.5000 90.0000 top

C5 10u C_0805 123.8250 -82.0000 90.0000 top

D1 LED_ALT LED_0603 132.2070 -80.2640 180.0000 top

L1 Ferrite_Bead_Small R_0603 120.5000 -90.6310 90.0000 top

P1 CONN_01X06 Pin_Header_Straight_1x06_Pitch2.54mm_SMD_Pin1Right 114.0675 -95.4630 0.0000 top

R1 1k R_0603 124.7140 -88.9000 270.0000 top

R2 1k R_0603 128.9050 -80.2640 0.0000 top

U1 LD3985M33R SOT-23-5 121.7150 -86.5670 90.0000 top

U2 4050 SO-16-N 122.0500 -101.8500 270.0000 top

## End

The above link also leads to free, open source programs for Windows and Linux KiCad Librarian which

enables, amongst other things, superimposed visual comparisons

between footprints in the same or different libraries, and another

program for creating drill files from KiCad projects. (However,

in October 2017, KiCad Librarian does not display the curved corners of

the rounded rectangle pads I am using.)

Here is my current thinking, in early-November 2017, based the above-mentioned document pcblib2013 and discussion thread00 and initial discussions on the KiCad mailing list early in 2016 - #thread01: https://groups.yahoo.com/neo/groups/kicad-users/conversations/topics/21460 .

As far as I can see there is a clear choice of technical standards to comply with regarding SMT component centroids and zero rotation angles - the IPC 7351x series. First, my understanding of the history behind these.

The above is a summary of the relevant standards documents, but I don't actually need a standards document to create my library footprints.

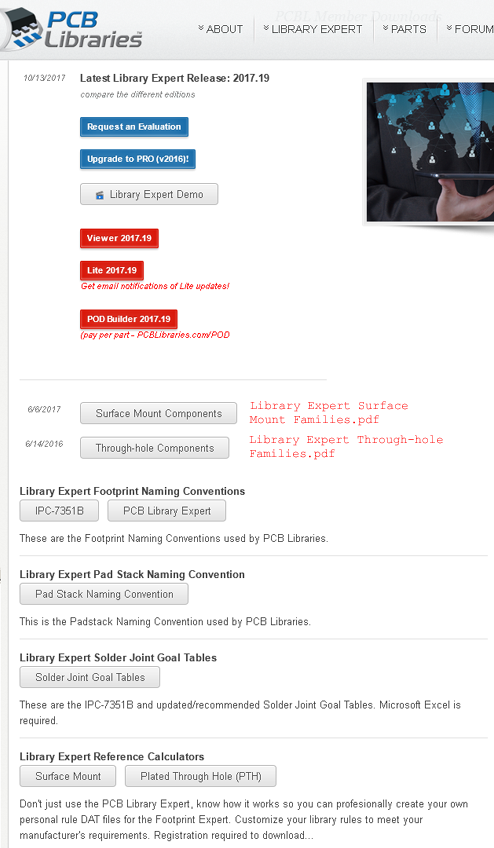

#2docs

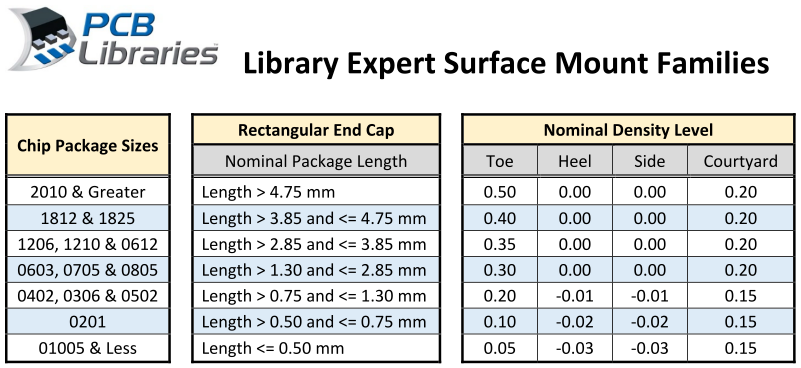

The two documents Library Expert Surface Mount Families.pdf and Library Expert Through-hole Families.pdf tell me a lot of what I need to know:

Before going any further, on 2017-10-19 I downloaded and installed the latest KiCad nightly (development version) from:

Later I installed kicad-r8665.e5c4cfc3b-x86_64.exe 01-Nov-2017

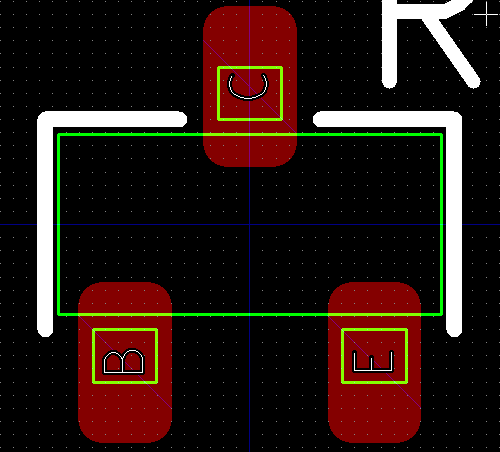

These nightlies' Footprint Editor supports rounded rectangle pads:

Next I made two attempts at making sure this 0805 (EAI imperial name) resistor footprint matches what is specified by IPC-7351 (in its current state of IPC-7351C almost being released), which is the basis of both Library Expert Through-hole Families.pdf and Library Expert Lite (as described below).

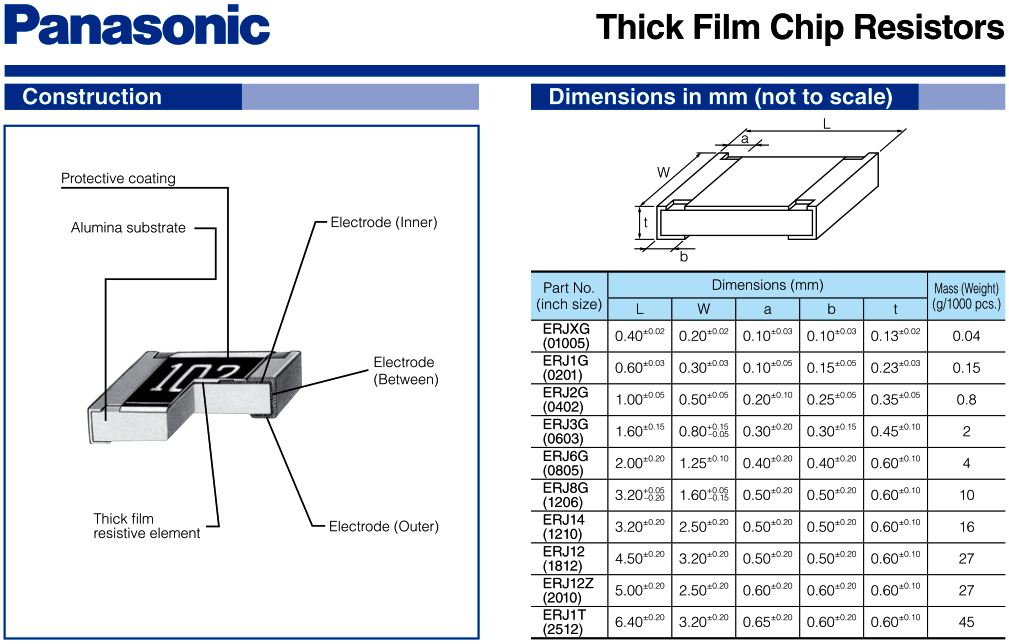

For the dimensions of the 0805 device itself, I need overall dimensions and the length (or width) of the metal contacts. The first two can be found on many websites but the third is more obscure. I looked at:

and obtained a data sheet from there: RDA0000/AOA0000C301.pdf . A table there shows the length of the metal contact in column b:

There is an example below of these change. These changes are not the same as what changes I would make to a footprint file which followed the KiCad Library Conventions (see below), since such a file is somewhat different from the file generated by Library Expert Lite.

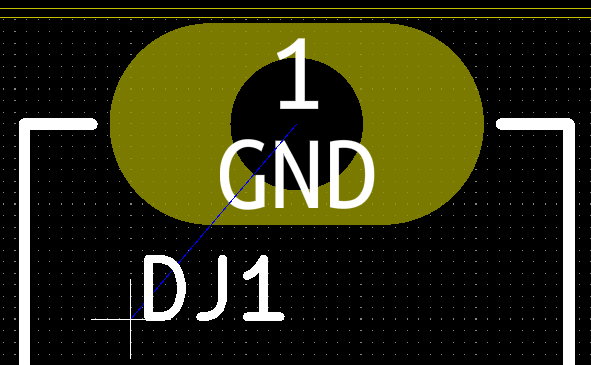

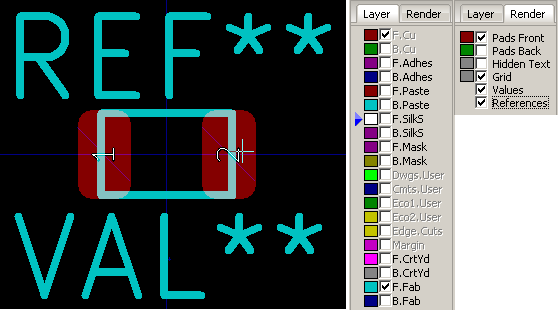

I understand that Mars_Warrior wants the F.Fab layer to produce a drawing which a PCB assembly company can use, so that every SMT component they are going to mount has an outline and the RefDes (reference) text. From this, they can look up all the details, such as part number, value (e.g. uF and voltage, or resistance, or a range of possible part numbers, each with links to suppliers websites) in the BoM file.

I understand he wants the Eco1.User layer to produce a similar drawing, for when he is hand-assembling a board. This has the same component outlines, but has the value instead - such as a simple resistance (2K7), capacitance (334), connector part number, microcontroller part number etc. - so he can instantly see what to place in each location. I think this is primarily for SMT components which are so small and densely packed that it may not be possible to have any text for many of them on the board itself (F.SilkS) and it would generally be impossible to have values on F.SilkS in addition to the reference text, even if there was room for the reference text.

It doesn't matter much how small the text is for reference and value on the F.Fab or Eco1.User layers since these are not part of the physical circuit board. It is easy to zoom on on these when looking at the computer monitor, or print these layers on large enough pieces of paper that the text can be read. With the silkscreen layer, the text really needs to be outside the body and pins of the component, whereas this is not a restriction on F.Fab, Eco1.User or other non-physical layers. So it is possible and desirable on the F.Fab and Eco1.User layers to have the outline of the component and the text of either the reference or the value, potentially inside the outline. In principle it might be possible and desirable to have both the reference (C12 etc.) and the value (104 etc.) on the same layer, but that could be cluttered and the part numbers or values can be very long.

According to the Pcbnew manual (2017-08-24 version), page 37:

This duplication of text does not suit my needs for a layer to send to PCBFast.com.au, which has lines to describe routed (milled) edges and text regarding this and perhaps other things. In principle I could choose to put this information on Dwgs.User, but that is already in use with the outlines of the components and their terminals (at least for the above example).

On this page, the purpose of the Fabrication layers is not clearly defined:

Following Mars Warrior's example I will use Eco1.User as he does, which leaves Eco2.User for my routing (milling) and other mechanical information, which is needed by the PCB fabricator.

The way I (and I think Mars Warrior and Joan Sparky, both of whom post to the KiCad forum) want to use KiCad appears to be different from the usage pattern supported by the KiCad library standard, formally known as the KiCad Library Convention, hereafter KLC (I am referring to rev 3.0.0 on 2017-11-03):

Until early November 2017, the KLC (rev 2.0.12) was here:

Section F5.2 (2017-11-04) requires that footprints in the footprint library that the F.Fab layer have three things for each footprint:

Section F5.1 (2017-11-04) requires that footprints in the footprint library that the F.SilkS layer has only one text item things for each footprint:

Now it is time to consider the mechanism of fp_text items in footprints, in the footprint library and for footprints in a PCB design within Pcbnew, as they are automatically placed, then then manually edited. This is quite tricky since I am considering several steps:

I am also thinking about how the footprint behaves when Pcbnew loads it from my footprint library (I currently have only one) into a PCB design due to manual placement, automatic placement due to loading a netlist - and how it behaves if the footprint is already in the PCB design but is somehow updated as a result of a netlist load. (To do: when does this occur???)

My primary interest is what state the footprint file must be in before being imported into Footprint Editor. What follows is based on my understanding of the program (Windows nightlies 2017-09-19 and 2019-11-01), various forum discussions and some source code :

Here is another perfectly valid text item:

There are three types of fp_text item:

Also of potential interest is this unofficial account of KiCad file formats from the author of VisualPlace:

which states, regarding the reference and value types of fp_text item:

From this, I observe:

Broadly speaking, there are three types of footprint file I am considering:

The 2017-19 version of Library Expert Lite does not produce anything for the Eco1.User layer. As I understand its options, the component outline, fp_text reference and fp_text value for the top of the PCB are all put on whatever KiCad layer we like - and F.Fab is the default - by way of the "Assembly Outline" line in the KiCad exporter options.

My understanding (late October 2017 with Library Expert Lite 2017-19 and a KiCad nightly from 2017-09-19) is:

Here is a table regarding the graphic elements (lines, arcs or circles etc.) representing the outline of the package in the footprints of several types.

These are the layers on which the footprints in my library have graphic elements - lines, arcs and circles - listed with the usual line width and their purpose.

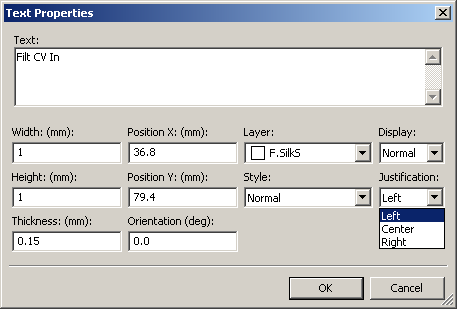

I also had to decide what arrangements my library components would have concerning where the cursor appears relative to a text item when moving it. In my PCB design I had made some such items place the cursor at the bottom left of the text, with this text in bold at the end of some fp_text items:

This suited me since I like to line up the bottom left of the text with a grid position:

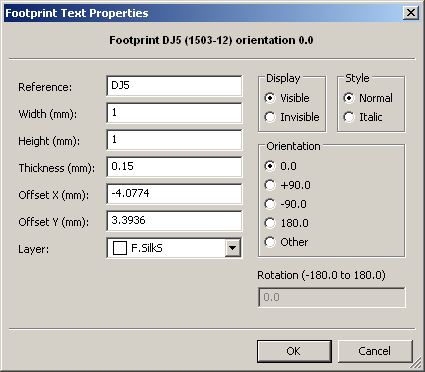

I am not sure how they got this way, since I couldn't find a way in Pcbnew of editing either the justification (left, center or right) or anything to do with top or bottom, using a Windows nightly from 2017-11-18. Editing one of these fp_text items involves a dialogue box:

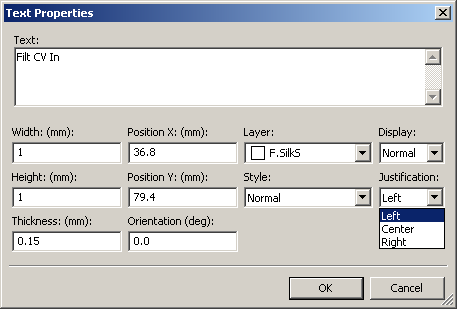

For free text items (not part of a footprint) there is a way of editing the justification to left, center or right:

Neither of these seem to provide a way of introducing bottom into this part of the PCB file.

For free text items, the "Display:" options are Normal and Mirrored. In the latter case, the PCB file contains:

I decided to change this way of working so that the cursor is (by default at least) centred both horizontally and vertically:

The reasons for this are:

This means that if I have two text items side-by-side, with differing text heights, and want the bottom edge of their characters to line up, then I will need to do some fancy manual editing or place them very finely with a 0.01mm grid, and get them at least this close - ten microns.

So I manually edited my PCB design file to get rid of all such justify constructs.

See a section below for some examples of SMT and through-hole footprints I generated using Library Expert Lite for my KiCad library. Before I could do this, I needed to sort out some other things mentioned in the following sections.

#footprintnames

Here is my current thinking, in early-November 2017, based the above-mentioned document pcblib2013 and discussion thread00 and initial discussions on the KiCad mailing list early in 2016 - #thread01: https://groups.yahoo.com/neo/groups/kicad-users/conversations/topics/21460 .

As far as I can see there is a clear choice of technical standards to comply with regarding SMT component centroids and zero rotation angles - the IPC 7351x series. First, my understanding of the history behind these.

IPC-SM-782A 1993, with amendments 1 and 2 in 1996 and 1999 respectively.

Superseded by IPC-7351.

IPC-7351 2005-02 (link) Superseded by IPC-7351A.

IPC-7351A 2007-02 (link) Superseded by IPC-7351B.

IPC-7351B 2010-01 (link) This seems to be the current (October 2017) version of the standard. However, according to a 2015-05-08 presentation by Tom Hausherr, CEO and founder of pcblibraries.com , there will be an IPC-7351C: http://www.ocipcdc.org/archive/What_is_New_in_IPC-7351C_03_11_2015.pdf and https://www.cskl.de/fileadmin/downloads/PCBLIBRARIES/Documentation/What-is-New-in-IPC-7351C_.pdf .

IPC-7351C This has not yet (2017-10-21) been finalised. Various documents about it can be found on the Web by searching for "What's new in IPC-7351C" such as #wnipc7351c https://www.cskl.de/fileadmin/downloads/PCBLIBRARIES/Documentation/What-is-New-in-IPC-7351C_.pdf . The latest news I could find on its slow progress (since 2012), and the degree to which its new contents have been incorporated into software and other documents, is this discussion #thread02, in which the last message was on 2016-11-01: https://www.pcblibraries.com/forum/ipc7351c-draft-or-release-date_topic1818.html

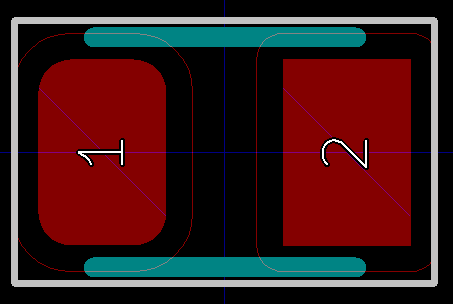

In the above-mentioned thread01 I mentioned some of the new features of IPC-7351C, including pads shaped as rounded rectangles. KiCad release versions cannot yet (4.0.7 in November 2017) support rounded rectangles. Such pads apparently have an advantage of greater reliability in reflow soldering.

According to this #thread03 https://github.com/KiCad/kicad-library/issues/1137 in April 2017, rounded rectangles (roundrect) will not appear in KiCad until version 5 is released, but they are supported by the nightlies (compilations of the development version of the whole KiCad project done every day, with bleeding edge code).

In thread01, regarding the "What's new" document, I wrote:

http://tinymicros.com/wiki/File:IPC-SM-782A.pdf

https://www.pcb-3d.com/wordpress/wp-content/uploads/ipc-sm-782a_amendment_1_and_2.pdf

https://www.pcb-3d.com/wordpress/wp-content/uploads/ipc-sm-782a_amendment_1_and_2.pdf

Superseded by IPC-7351.

IPC-7351 2005-02 (link) Superseded by IPC-7351A.

IPC-7351A 2007-02 (link) Superseded by IPC-7351B.

There is a document from this time,

which some people writing on PCB forums quote as one they refer

to. It is from ipc.org, the IEC and pcblibraries.com Electronic Component Zero Orientation For CAD Library Construction, available here http://ohm.bu.edu/~pbohn/... . (This is not to be confused with a standard with a similar name, most recently from 2017: IEC 61188-7-2017.)

The PDF date is 2007-11-30. It mentions a set of standards

IPC-7351 to 7359, but there's no sign of 7352 and above at ipc.org now.

This document is not a standard, but contains lots of pertinent information from the time from the relevant standards. It doesn't mention IPC-7351A.

I think that the current (October 2017) version of the information in this document can be found in the members area of pcblibraries.com, as mentioned below #2docs. These are available after a free registration.

This document is not a standard, but contains lots of pertinent information from the time from the relevant standards. It doesn't mention IPC-7351A.

I think that the current (October 2017) version of the information in this document can be found in the members area of pcblibraries.com, as mentioned below #2docs. These are available after a free registration.

IPC-7351B 2010-01 (link) This seems to be the current (October 2017) version of the standard. However, according to a 2015-05-08 presentation by Tom Hausherr, CEO and founder of pcblibraries.com , there will be an IPC-7351C: http://www.ocipcdc.org/archive/What_is_New_in_IPC-7351C_03_11_2015.pdf and https://www.cskl.de/fileadmin/downloads/PCBLIBRARIES/Documentation/What-is-New-in-IPC-7351C_.pdf .

IPC-7351C This has not yet (2017-10-21) been finalised. Various documents about it can be found on the Web by searching for "What's new in IPC-7351C" such as #wnipc7351c https://www.cskl.de/fileadmin/downloads/PCBLIBRARIES/Documentation/What-is-New-in-IPC-7351C_.pdf . The latest news I could find on its slow progress (since 2012), and the degree to which its new contents have been incorporated into software and other documents, is this discussion #thread02, in which the last message was on 2016-11-01: https://www.pcblibraries.com/forum/ipc7351c-draft-or-release-date_topic1818.html

In the above-mentioned thread01 I mentioned some of the new features of IPC-7351C, including pads shaped as rounded rectangles. KiCad release versions cannot yet (4.0.7 in November 2017) support rounded rectangles. Such pads apparently have an advantage of greater reliability in reflow soldering.

According to this #thread03 https://github.com/KiCad/kicad-library/issues/1137 in April 2017, rounded rectangles (roundrect) will not appear in KiCad until version 5 is released, but they are supported by the nightlies (compilations of the development version of the whole KiCad project done every day, with bleeding edge code).

In thread01, regarding the "What's new" document, I wrote:

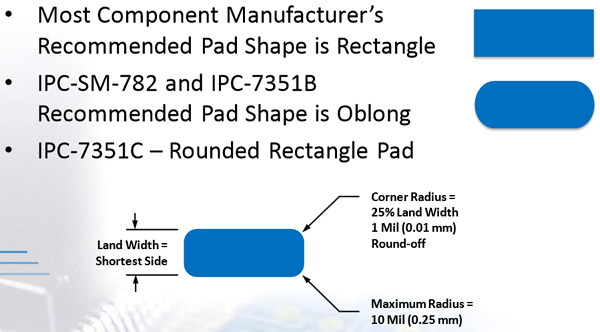

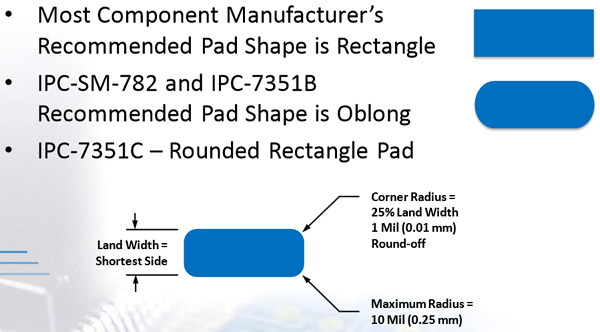

Previously, the recommended pad shape

was "oblong" - the longer sides straight with the shorter sides being

rounded as 180 degree sections of a circle. As far as I know, this is

the same as an "oval" pad in Kicad.

For IPC-7351C, rounded rectangle SMT pads are recommended, where the corner radius is at most 0.25mm and otherwise is 25% of the width (shortest side) of the otherwise rectangular pad. So on the shorter sides, the middle 50% is straight and the end 25% sections are 90 degree

sections of a circle.

For IPC-7351C, rounded rectangle SMT pads are recommended, where the corner radius is at most 0.25mm and otherwise is 25% of the width (shortest side) of the otherwise rectangular pad. So on the shorter sides, the middle 50% is straight and the end 25% sections are 90 degree

sections of a circle.

The above is a summary of the relevant standards documents, but I don't actually need a standards document to create my library footprints.

#2docs

The two documents Library Expert Surface Mount Families.pdf and Library Expert Through-hole Families.pdf tell me a lot of what I need to know:

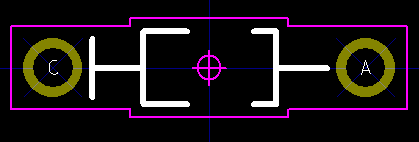

- How to name pads, such as 1 and 2 for a resistor, and C and A for a diode.

- How to orient the footprint in terms of centroid and initial rotation.

- What dimensions to use for the toe, heel and side aspects of each pad, which define the PCB pad edges relative to the size of the part of the IC, resistor, etc. package which is to be soldered.

Before going any further, on 2017-10-19 I downloaded and installed the latest KiCad nightly (development version) from:

Later I installed kicad-r8665.e5c4cfc3b-x86_64.exe 01-Nov-2017

These nightlies' Footprint Editor supports rounded rectangle pads:

Next I made two attempts at making sure this 0805 (EAI imperial name) resistor footprint matches what is specified by IPC-7351 (in its current state of IPC-7351C almost being released), which is the basis of both Library Expert Through-hole Families.pdf and Library Expert Lite (as described below).

For the dimensions of the 0805 device itself, I need overall dimensions and the length (or width) of the metal contacts. The first two can be found on many websites but the third is more obscure. I looked at:

and obtained a data sheet from there: RDA0000/AOA0000C301.pdf . A table there shows the length of the metal contact in column b:

With length being X and width being Y, the figures are:

Length 2.00mm.

Width 1.25mm.

Contact length 0.40mm.

Height of contact (t) 0.60mm.

Width 1.25mm.

Contact length 0.40mm.

Height of contact (t) 0.60mm.

1 - Using Library Expert Through-hole Families.pdf #2docs

For the "normal" density level, this PDF provides the details I need to set the size and locations of the solder pads:

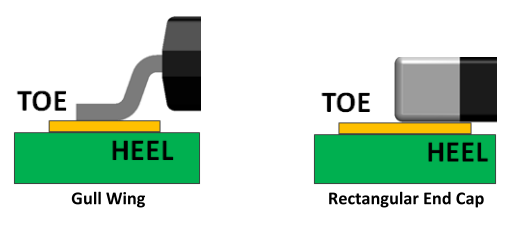

Page 37 shows the meaning of Toe and Heel in the context of SOIC, SOT etc. components (left diagram) and chip resistors and capacitors etc. (right diagram):

Side refers to how much further the solder pad must extend beyond the contact terminal in the directions of the arrow marked W in the Panasonic diagram.

Courtyard is defined, in IPC-7351 (2005) as:

For an 0805, the centre of the courtyard lines must be 0.2mm outside the edges of the pads.

I did some pen and paper calculations and arrived at the two pads being:

The figures in the above table were chosen for 8 size ranges of chip resistors, based on knowledge of their thickness, overall size and power dissipation. So there is no explicit mention of the thickness (t in the Panasonic table) of 0.60mm.

There may be an IPC specification for the minimum distance between any part of the component legend (AKA "silkscreen" - identifying text and/or the lines which indicate the outline of the device), but I was not sure where to look. I chose 0.15mm based on Seeed Studio's PCB Design for Manufacture 1.1 (June 2017) document (see below: #seeestudiodfm), page 7. They also state that the minimum height of text for the silkscreen is 0.60mm and the minimum thickness of the silkscreen lines, including those which make up the text, is 0.10mm.

So I designed a footprint from scratch, retaining KiCad's default 1.00mm high text with 0.15mm lines.

I won't describe this any further, because I think the second technique, using Library Expert Lite, is better. However, it does illustrate to some degree that it is possible to create footprints manually in KiCad which are technically correct, follow recognised standards for pad size, pin numbering, initial orientation etc. all based on a freely available document which is up-to-date with the current state of the art standards, the yet to be released IPC-7351C.

Side refers to how much further the solder pad must extend beyond the contact terminal in the directions of the arrow marked W in the Panasonic diagram.

Courtyard is defined, in IPC-7351 (2005) as:

The smallest rectangular area that

provides a minimum electrical and mechanical clearance (courtyard

excess) around the combined component body and land pattern boundaries.

For an 0805, the centre of the courtyard lines must be 0.2mm outside the edges of the pads.

I did some pen and paper calculations and arrived at the two pads being:

0.70mm long (X),

1.25mm wide (Y)

1.20mm (X) gap between them.

So the centres are 1.90mm (X) apart, each with an offset of 0.95mm (X) from the centroid.

The courtyard is a rectangle 2.8mm long (X) and 1.6mm wide (Y).1.25mm wide (Y)

1.20mm (X) gap between them.

So the centres are 1.90mm (X) apart, each with an offset of 0.95mm (X) from the centroid.

The figures in the above table were chosen for 8 size ranges of chip resistors, based on knowledge of their thickness, overall size and power dissipation. So there is no explicit mention of the thickness (t in the Panasonic table) of 0.60mm.

There may be an IPC specification for the minimum distance between any part of the component legend (AKA "silkscreen" - identifying text and/or the lines which indicate the outline of the device), but I was not sure where to look. I chose 0.15mm based on Seeed Studio's PCB Design for Manufacture 1.1 (June 2017) document (see below: #seeestudiodfm), page 7. They also state that the minimum height of text for the silkscreen is 0.60mm and the minimum thickness of the silkscreen lines, including those which make up the text, is 0.10mm.

So I designed a footprint from scratch, retaining KiCad's default 1.00mm high text with 0.15mm lines.

I won't describe this any further, because I think the second technique, using Library Expert Lite, is better. However, it does illustrate to some degree that it is possible to create footprints manually in KiCad which are technically correct, follow recognised standards for pad size, pin numbering, initial orientation etc. all based on a freely available document which is up-to-date with the current state of the art standards, the yet to be released IPC-7351C.

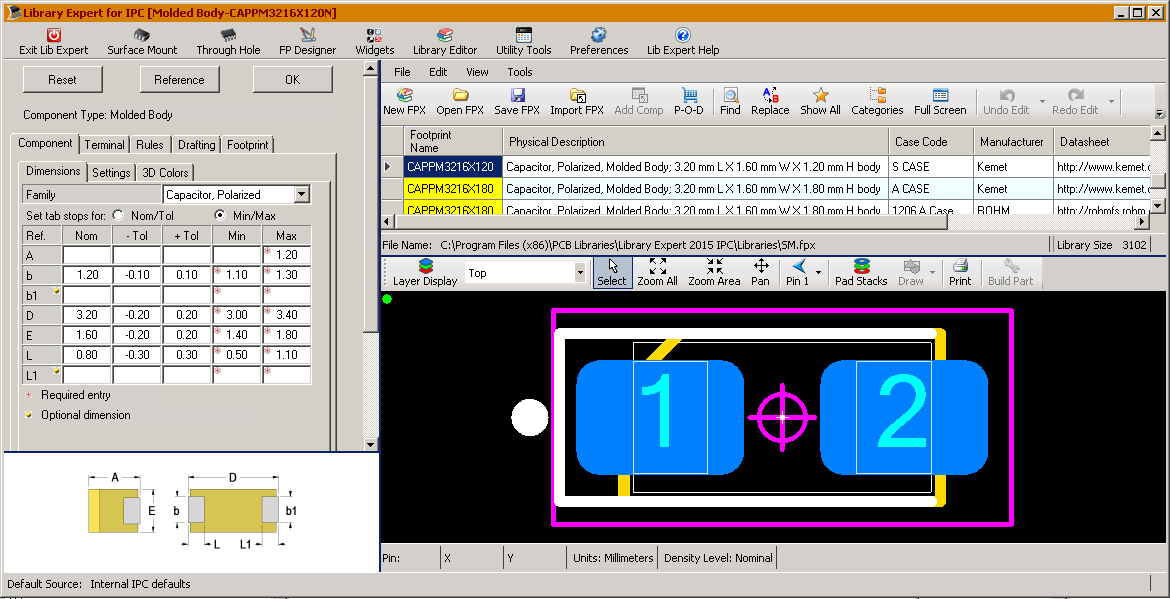

2 - Using Library Expert Lite

According to this #thread04 https://forum.kicad.info/t/kicad-pcb-library-expert/2232/8

Library Expert Lite has been able to export to KiCad since early

2016. In this thread, bobc wrote that he found the EULA for

Library Expert Lite too restrictive, but he didn't cite the text he was

referring to.

To find the EULA for a particular version of the program, use a URL such as: https://www.pcblibraries.com/Downloads/FPX!Library_Expert_2017-19_Lite.asp

with the appropriate year and version number. This is the start of a download procedure for registered users, and assuming your browser cookies reflect that fact that you are a user, you should see the EULA. Also, the EULA text is included with the zip file which includes the installer. The 2017-19 EULA starts with "Updated on May 2, 2017".

#libexpeula The only restriction I can find in the EULA regarding what we do with the footprints generated by PCB Library Expert Lite is:

The footprint file I generated, as described below, did not contain any such data. "PCB Libraries" did not appear in this file.

This page http://www.pcblibraries.com/products/compare/ indicates that the Lite version contains adware and requires an Internet connection to function. Regarding use of the Lite program, the EULA's restrictions are light compared to the single computer requirements for the paid-for Pro version:

I got the impression from bobc's comments that there was some restriction on how the footprints could be used, such as disallowing them, or any footprint derived from them, being sent to some individual or company other than the user, such as for a publicly available library. However, I see no such restriction in the current EULA.

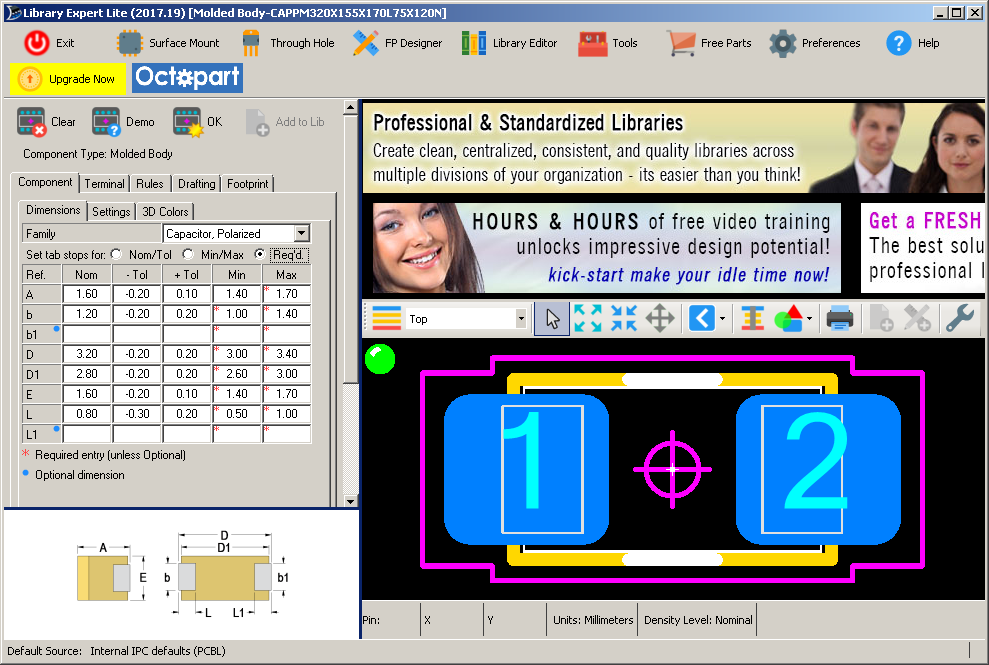

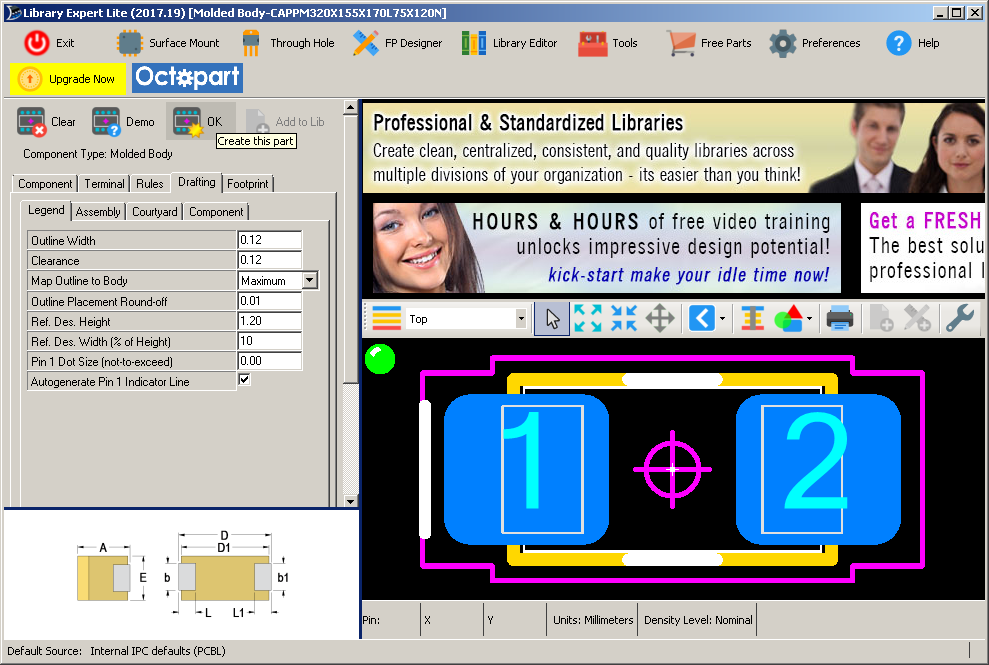

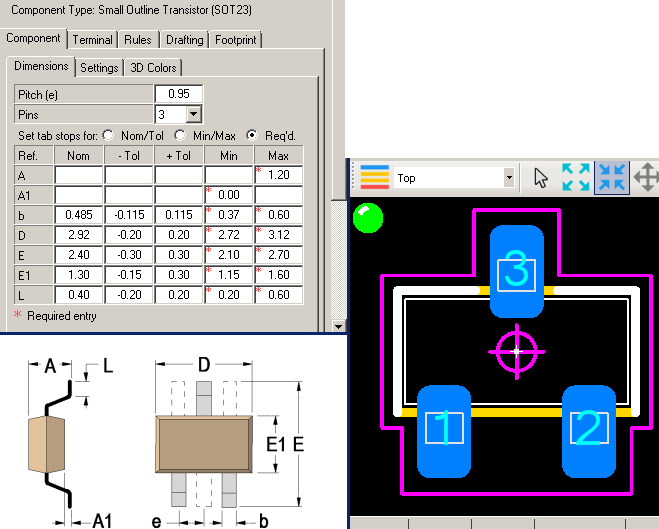

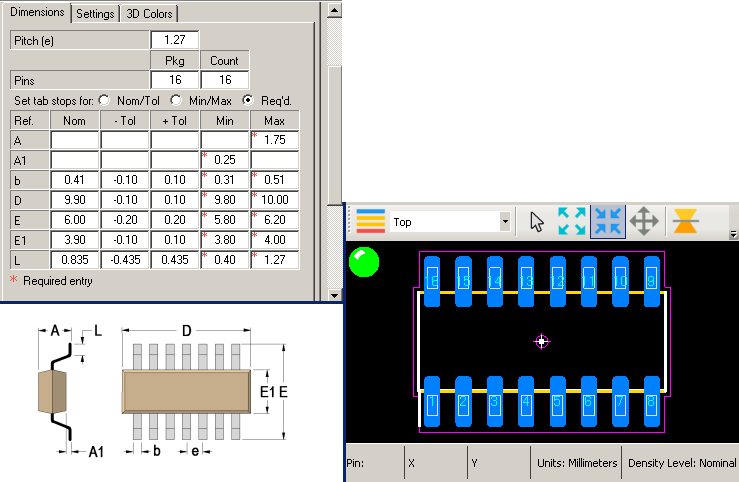

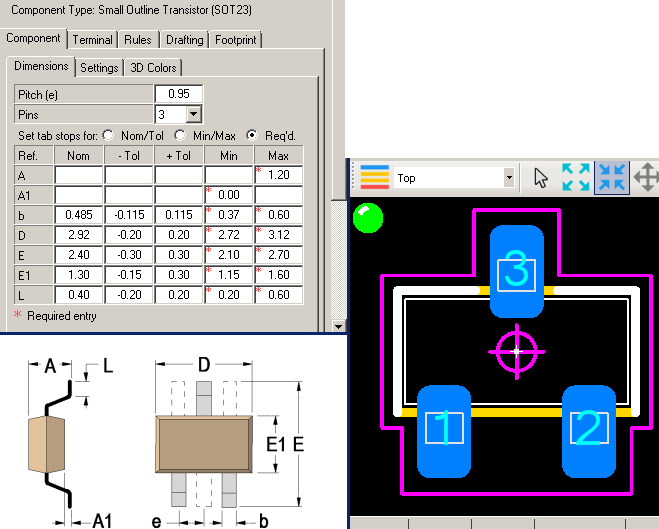

The steps required to generate a KiCad 0805 footprint using Library Expert Lite 2017.19 are:

Here are some of the details of how I did it.

I installed Library Expert Lite (2017.19) (as it calls itself once running) which I downloaded as Library_Expert_2017-19_Lite.zip from:

This is available for Windows only and I ran it on Windows 7 Prof. 64 bit. Since this URL changes for each release, you can find the URL for the latest release from the above-mentioned version history section of the forum, or by using the above-mentioned memberdownloads.asp URL.

The Lite version's capabilities are listed at http://www.pcblibraries.com/products/compare/ in comparison to those of the Pro version for KiCad https://www.pcblibraries.com/Products/FPX/KiCad.asp which costs USD$624 for a single user perpetual license. (Though resellers may have lower prices, such as this page which may be out of date.)

Here are the actions I took to make the footprint and export it, written as instructions for you to follow.

To find the EULA for a particular version of the program, use a URL such as: https://www.pcblibraries.com/Downloads/FPX!Library_Expert_2017-19_Lite.asp

with the appropriate year and version number. This is the start of a download procedure for registered users, and assuming your browser cookies reflect that fact that you are a user, you should see the EULA. Also, the EULA text is included with the zip file which includes the installer. The 2017-19 EULA starts with "Updated on May 2, 2017".

#libexpeula The only restriction I can find in the EULA regarding what we do with the footprints generated by PCB Library Expert Lite is:

Lite

version output files may be altered, but removal or alteration of the

auto-inserted "PCB Libraries" meta data from any output files is a

violation of this Agreement.

The footprint file I generated, as described below, did not contain any such data. "PCB Libraries" did not appear in this file.

This page http://www.pcblibraries.com/products/compare/ indicates that the Lite version contains adware and requires an Internet connection to function. Regarding use of the Lite program, the EULA's restrictions are light compared to the single computer requirements for the paid-for Pro version:

LITE

and VIEWER - This Agreement entitles you to install and use the limited

"Lite" and "Viewer" versions of the Software Product on any number of

your computers. There are no restrictions on number of installations

for the "Lite" and "Viewer" versions.

I got the impression from bobc's comments that there was some restriction on how the footprints could be used, such as disallowing them, or any footprint derived from them, being sent to some individual or company other than the user, such as for a publicly available library. However, I see no such restriction in the current EULA.

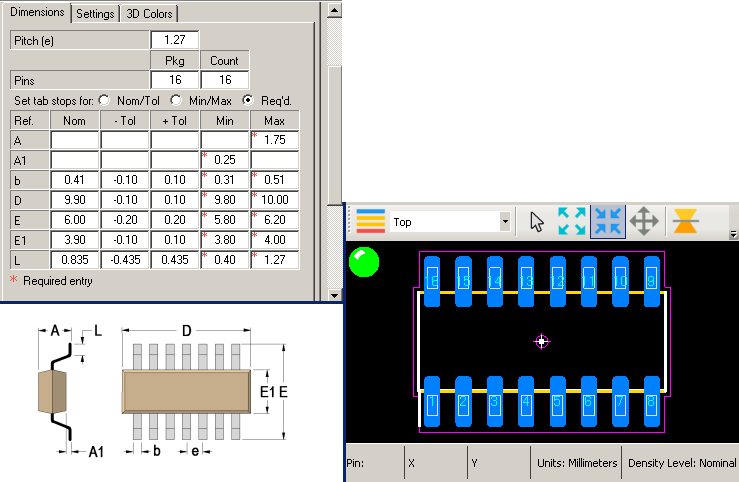

The steps required to generate a KiCad 0805 footprint using Library Expert Lite 2017.19 are:

- Manually look up the dimensions of the device itself, as described above using the Panasonic data sheet.

- Manually enter these into Library Expert Lite and click various

buttons. This will produce a footprint inside the program, which

can be viewed.

- One any necessary adjustments are made, this can be exported as a KiCad.mod file.

In principle it can be saved in a library, but I had difficulty getting

KiCad's Footprint Editor to recognise the new arrival, so I exported it

to a separate directory, and imported that file into Footprint Editor.

- There are a number of things to change and clean up, such as

making SMT pads rounded rectangles.

- Then the footprint can be saved into a library.

Here are some of the details of how I did it.

I installed Library Expert Lite (2017.19) (as it calls itself once running) which I downloaded as Library_Expert_2017-19_Lite.zip from:

This is available for Windows only and I ran it on Windows 7 Prof. 64 bit. Since this URL changes for each release, you can find the URL for the latest release from the above-mentioned version history section of the forum, or by using the above-mentioned memberdownloads.asp URL.

The Lite version's capabilities are listed at http://www.pcblibraries.com/products/compare/ in comparison to those of the Pro version for KiCad https://www.pcblibraries.com/Products/FPX/KiCad.asp which costs USD$624 for a single user perpetual license. (Though resellers may have lower prices, such as this page which may be out of date.)

Here are the actions I took to make the footprint and export it, written as instructions for you to follow.

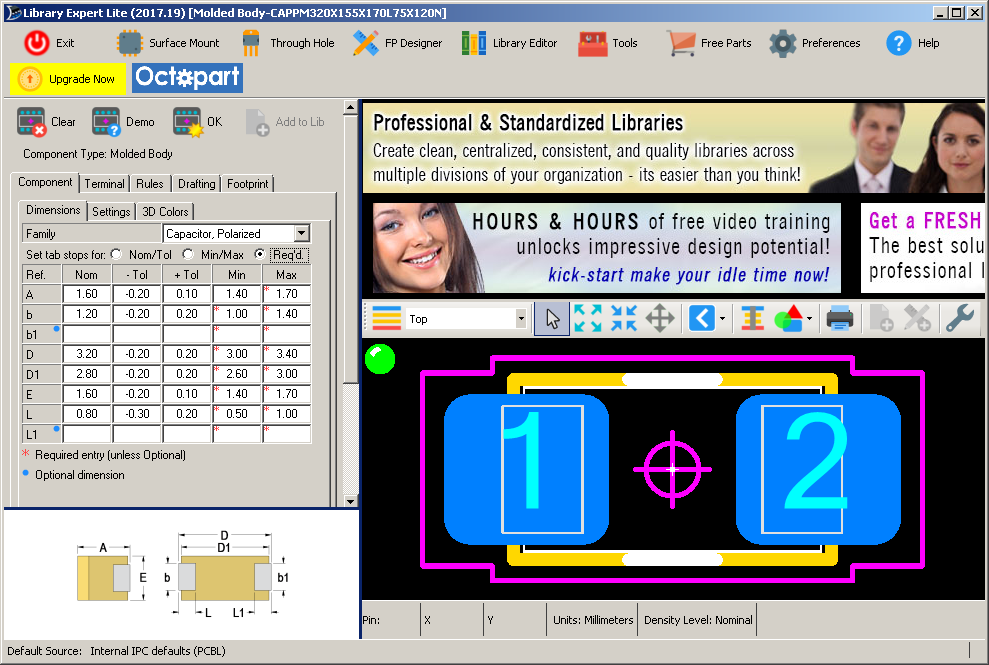

- Click the "Surface Mount" button at the top.

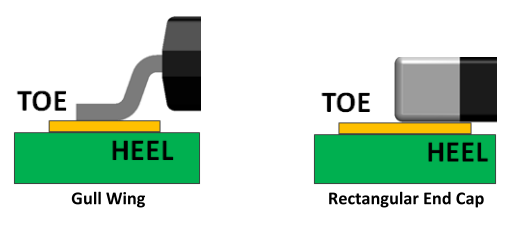

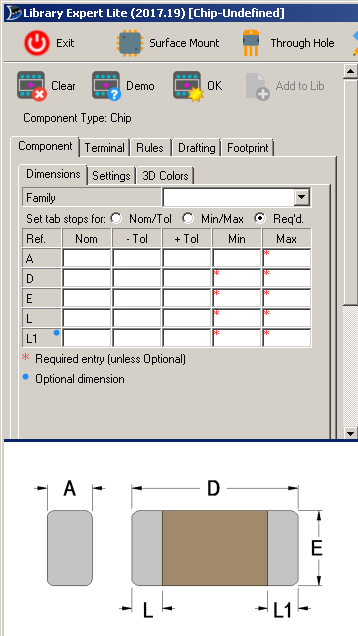

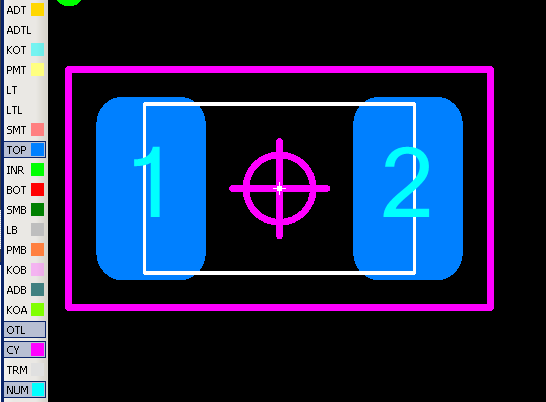

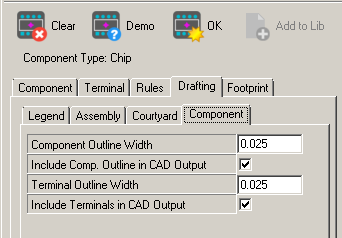

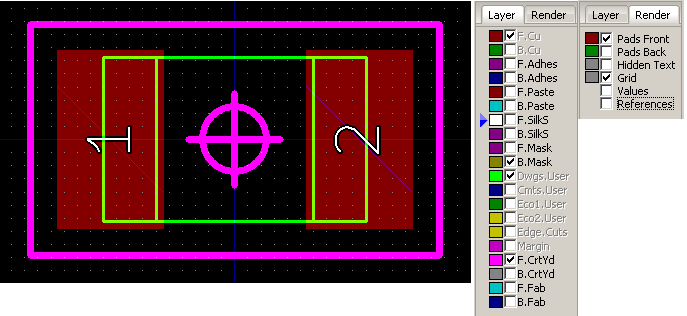

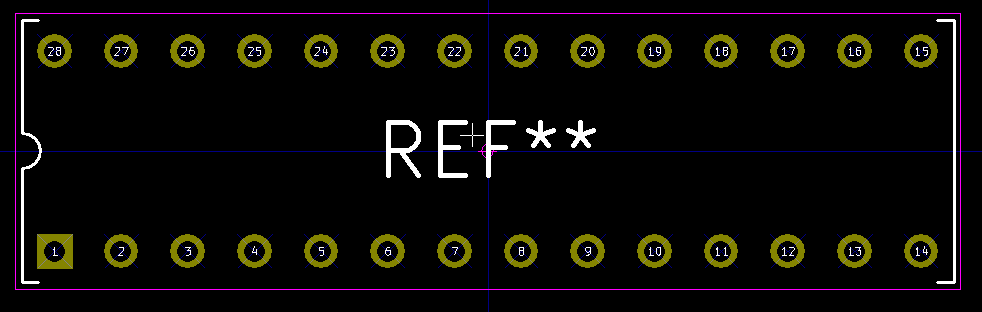

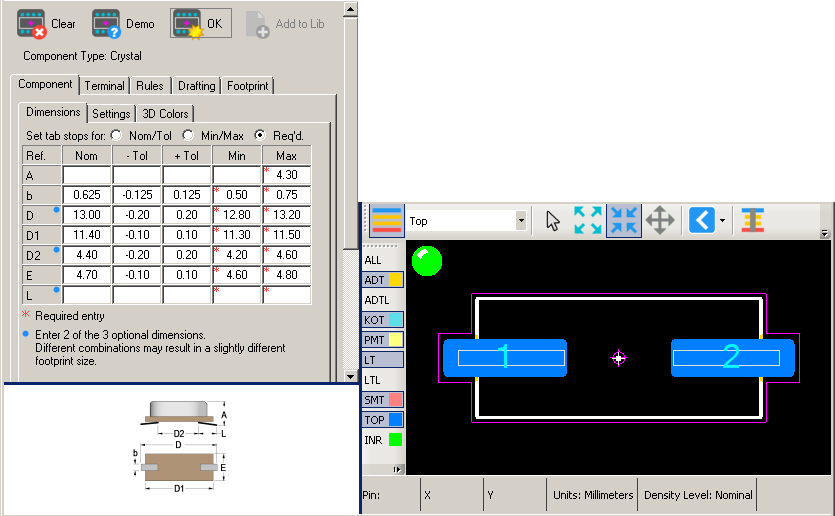

- From the list at the left, select "Chip" and click the "OK" button. This results in:

- Click the "Nom/Tol" radio button, enter the device dimensions,

four values from the Panasonic data sheet into the "Nom" column, for

rows A, D, E and L:

A = 0.60 = height (Z) of the resistor, from the t column of the data sheet.

D = 2.00 = length (X) of the resistor, from the L column.

E = 1.25 = width (Y) of the resistor, from the W column.

L = 0.40 = length (X) of the electrical contact, from the b column.

Then for those rows in the "- Tol" column, enter 0. In the "Family" pull-down list, select "Resistor". The result, for me, appeared as:

- Click the "OK" button. This will generate an updated

graphic display of the footprint, and seems to be necessary if we want

to change some items in other tabs and sub-tabs.

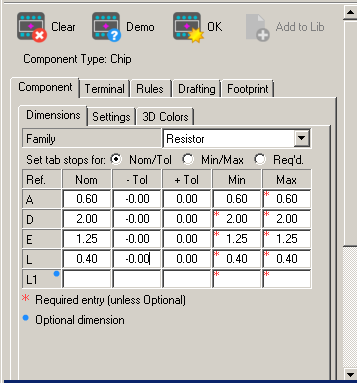

- This next step can be omitted - this is to show where we choose

the density level, which is how compact the software makes our

footprint. Click on the Terminal tab and then its Density Level sub-tab. The default is Nominal (N) which is what I want. The other options are Most and Least, and the actual values these presets control can be fine-tuned.

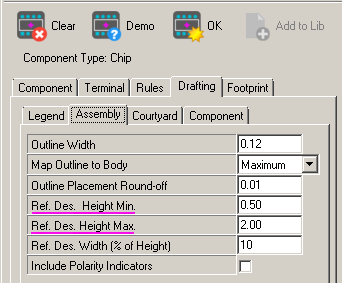

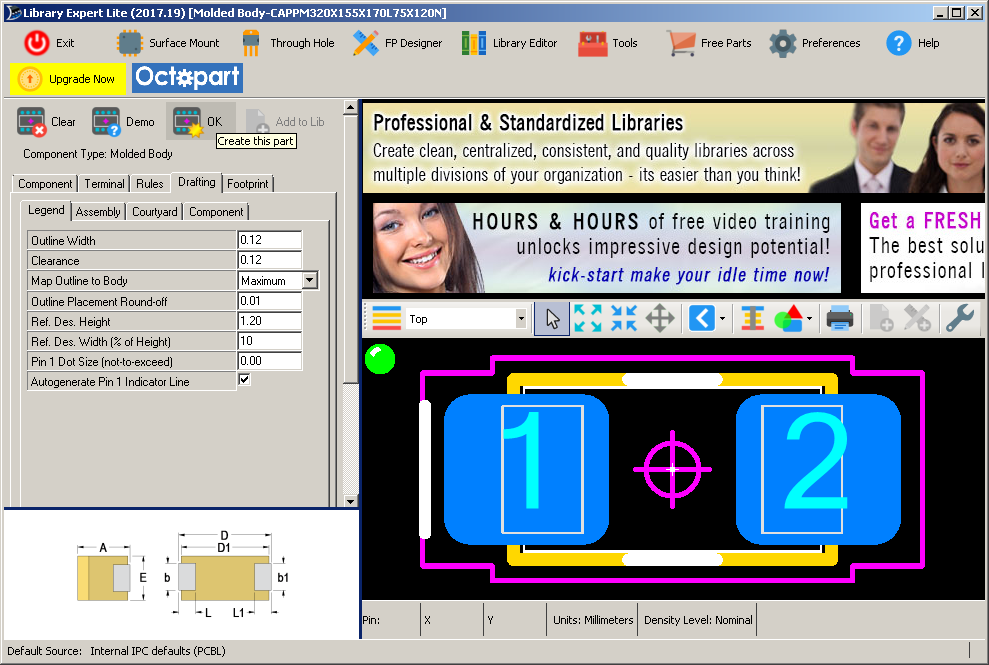

- This next step can be omitted - this is to show where we could

choose

the height and line-thickness of the silkscreen component legend text

and I think the lines on this layer which depict the outline of the

component. (I later decided to set the text size and line widths with

=a direct edit of the footprint file exported by Library Export Lite,

rather than relying on Library Expert Lite's settings - each of which

has to be manually set again for every fresh footprint which is

generated.) Click on the Drafting tab and then its Legend sub-tab. The defaults are presumably from IPC-7531: Outline Width from 0.12 to 0.10 and Ref. Des. Height from 1.20 to 1.00.

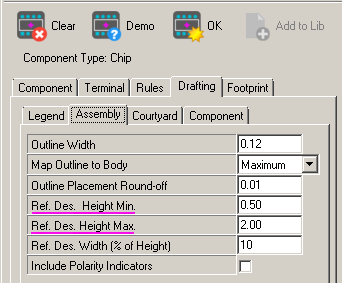

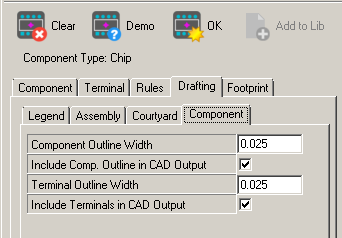

The sub-tab Assembly has similar settings for a rectangle which will be on KiCad's F.Fab layer, for an assembly drawing which shows the outline of the resistor.

The sub-tab Courtyard concerns a rectangle (or something more complex for larger, more complex-shaped components) which will be drawn on KiCad's F.CrtYd Courtyard layer, as well as an optional, default-on, cross-hair with circle ("target") at the X = 0, Y = 0 position (AKA the centroid). I didn't change anything. I am not sure that "Expand Courtyard to Include Legend" should be ticked, but it made no difference in this instance.

The sub-tab Component has settings for a set of thin lines which will be on KiCad's Dwgs.User layer. The lines create three rectangles in this example, one for the outline of the whole resistor and one each for each electrical terminal (contact).

Now select the Components tab again, with its Dimensions sub-tab, as depicted above.

- Click the "OK" button.

- If all is well, there will be no error message and the main

display window will show the footprint, with no grid or scale (but the

cursor can be used to show coordinates) and without some text items

which will appear in the exported KiCad footprint:

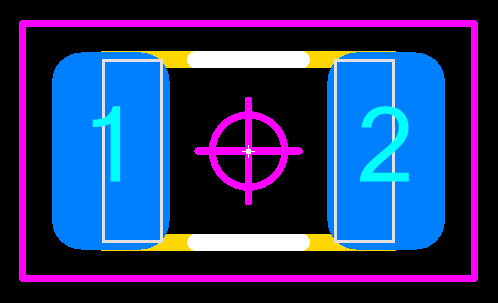

The pull-down list at the top left of this section of the window enables us to select something about the order the layers are drawn, but I don't yet understand it. The icon to its left, with four coloured bars, opens up a side-bar where we can choose the colours of the layers and whether they are on or off. See my cheatsheet0 image below. The above image results from the default layer on-and-off settings and with the default colours.

- Click the spanner icon at the right of the toolbar over the

display window. (If

you get an error such as one announcing an unhandled exception

regarding "Name

cannot begin with the '3' character, hexadecimal value 0x33. Line 3,

position 321." then this may be due to a line in a config file in the

program's installation directory, which for me: C:\Program Files

(x86)\PCB Libraries\Library Expert Lite 2017\FPXFormatPreferences.xml

. The program writes a keyword "3D_TOP" in the KiCad exporter

information, which it later objects to. This bug was fixed in the

release of 2017-19 available after about 2017-10-25, so you should be

able to avoid this by deleting the file or at least editing the keyword

to "THREED_TOP" and installing the bug-fixed version.)

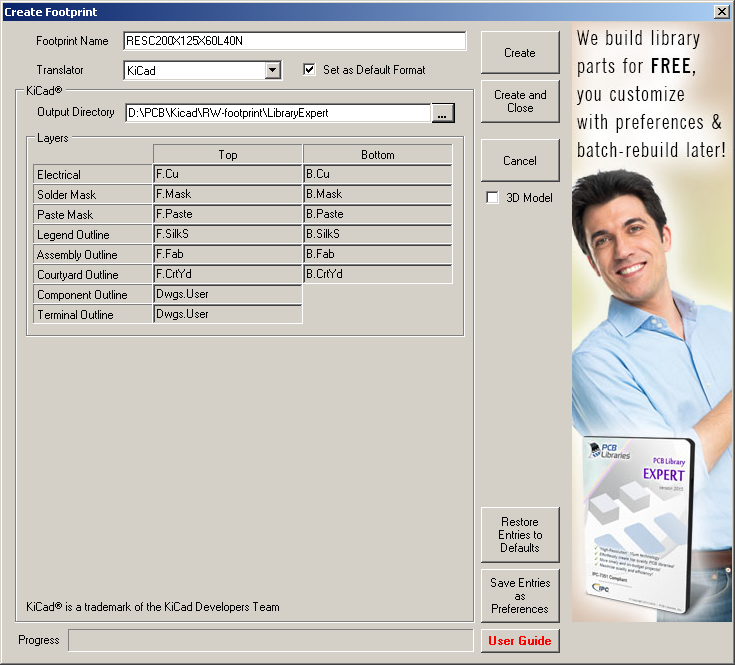

- Select the "Translator" as "KiCad". I also selected "Set as Default Format".

- Select the output directory. Then the dialogue box should

look like this. The Top and Bottom layer names can be altered if

desired.

- Press the "Create" button. For me, this causes a file RESC200X125X60L40N.kicad_mod to be written to the output directory. This can be imported into Footprint Editor.

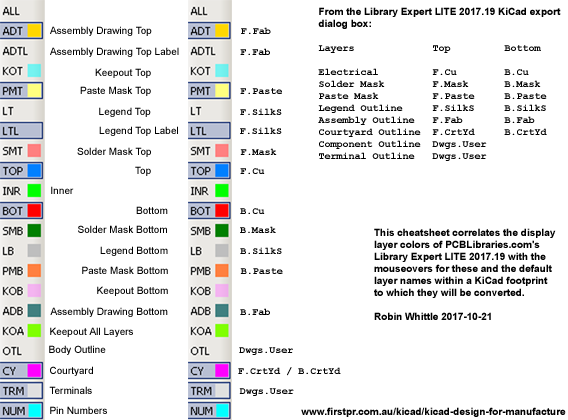

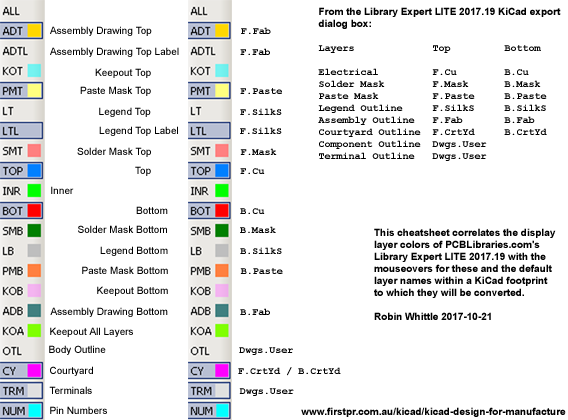

#cheatsheet0

Here is a cheatsheet correlating the default colours of Library Expert's layers, with their mouseover texts and the default layers they correspond to when the footprint is converted to a KiCad file. The full resolution version is: library-expert-layer-colours.png .

The last item NUM does not seem to be a layer, but enables the display of the pad numbers over the top of everything else. Right-clicking the colour box enables us to change the colour - except that some items such as ADTL do not have a colour, since this is set by the ADT item.

Three extra items appear (at least sometimes, for me) below item NUM:

Here are some examples of the display with only particular layers turned on:

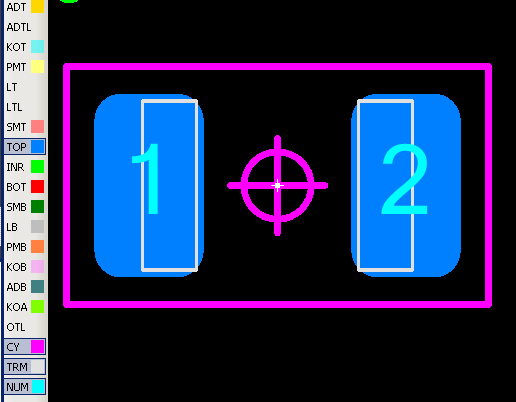

This shows the pads represented by Top copper (F.Cu) in blue, with pin numbers and the TRM layer showing the terminals. The magenta is Top Courtyard, which is converted to KiCad's F.CrtYd layer. The circle (target) and crosshairs can be turned off and resized in the various tab and sub-tabs mentioned above. The little white thing in the middle is not part of the footprint - this is Library Expert showing where 0,0 is.

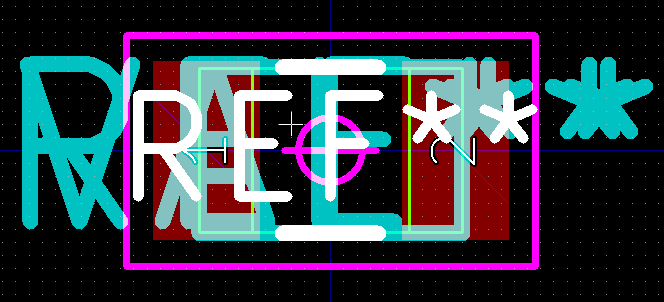

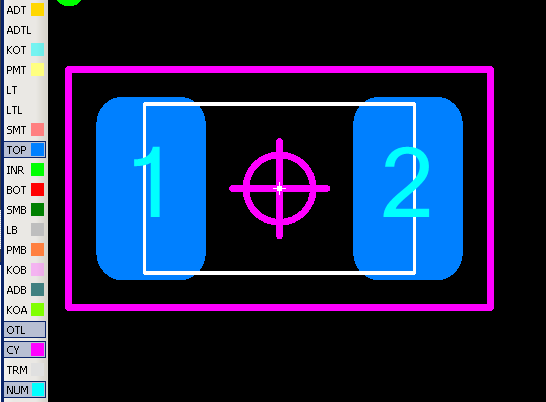

I turned off the terminals and turned on the Body Outline. Both these layers are converted to KiCad's Dwgs.User layer.

I understand the the Courtyard layer (there are front and back ones in KiCad) is used when laying out the PCB so that each component is kept a suitable distance from the other. I guess it may also be useful, with these crosshairs and targets, for the assembly company, but they should in principle be able to see where each component's centre is via the .POS file.

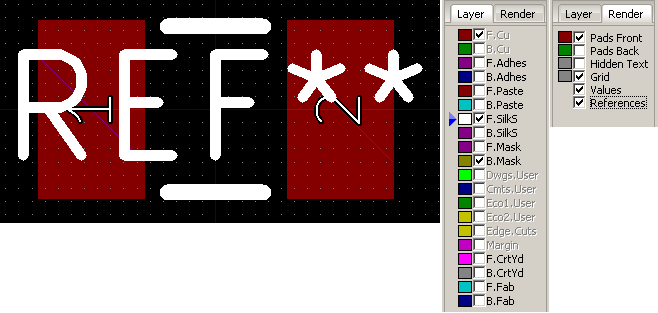

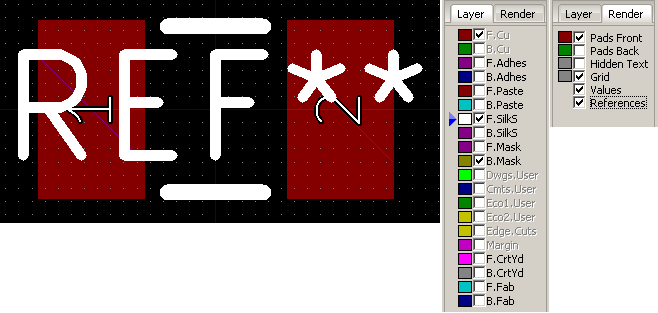

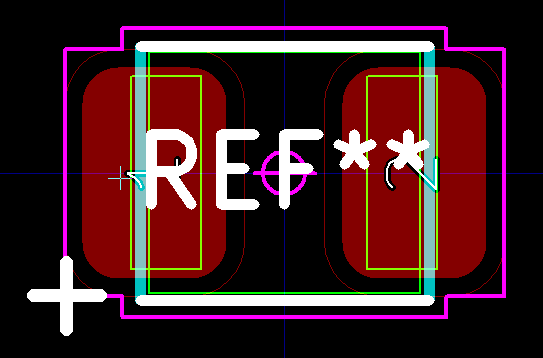

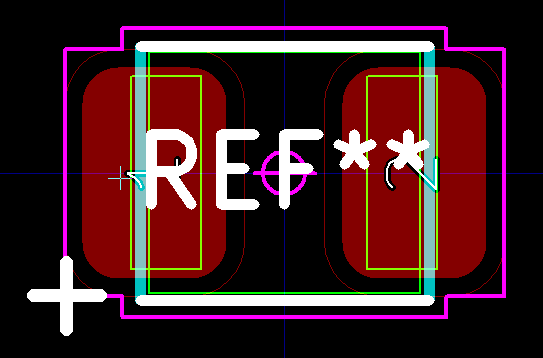

On top, because it was the most recent layer I turned on, is the Assembly Drawing Top's rectangle showing the outline of the resistor. The Assembly Drawing Top Label is depicted as well as Name, but all that matters to us is its orientation and position. This represents where two items will be in the converted footprint, both on the F.Fab layer, which is where the four lines of the rectangle will be as well: text value containing VAL** and text reference containing REF**. (See below for details of how KiCad interprets these fp_text items. From the exported footprint itself:

I was puzzled as to why the first item of text in the excerpt above is made so small: 0.77mm high. This is probably due to the fact that the whole component is small and the range of text sizes which are, by default in this program (presumably matching the specifications of the soon-to-be released IPC-7351C standard) set to 0.50mm to 2.00mm. This is in the Drafting tab > Assembly sub-tab:

Since my PCB fabricator http://www.pcbfast.com.au/techinfo/silkscreen-legends/ specifies for the silkscreen:

which preclude this part of the converted footprint from being used as is:

So the solution will be to alter these settings before creating components. This needs to be done for each component, as far as I know, with Library Expert Lite, but can be set in preference file for the Pro version.

#seeestudiodfm

Also, the widely-cited SeeedStudio document: http://www.seeedstudio.com/blog/2017/06/08/free-pcb-dfm-manual-v1-1-available-in-seeed-fusion/ states (page 7) that the silkscreen's minimum character height is 0.6mm and line width 0.1mm.

Once the footprint is placed in the PCB design, we can change these things manually, but it would probably be best to get the footprint in the library set so its default state doesn't violate the restrictions on what we can have made. These changes can be made in Footprint Editor, but it might be better to tweak Library Expert Lite to set the values within proper limits. (Later I decided to set the size of these text items on all layers to 0.8mm in a later edit of the footprint file, before importing it into Footprint Editor for review and saving to my library.)

There are three separate layers in this Library Expert system (for the top = front side) which correspond to the pad:

however they all show the same thing, in this example, and at least for this particular footprint, all three aspects of the pad are defined in a single line for each pad, all with the same size:

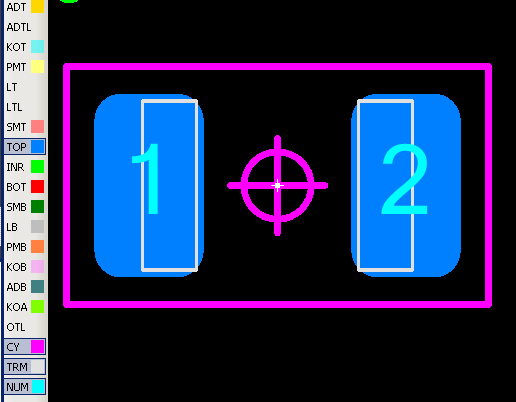

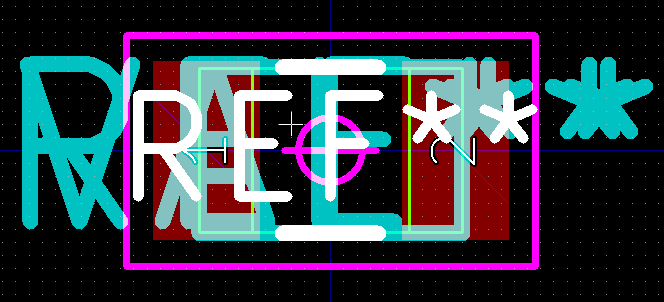

Here is the image which results from the final combination of layers turned on:

The two lines are the silkscreen indication of the location of the resistor. Other footprints have more elaborate arrangements, including the presence or absence of a line within this shape to indicate polarity (the location of pin 1, or the positive terminal etc.) - or alternatively the presence of a dot to indicate this. IPC-7351C specifies that no part of the silkscreen image should be in the same place, or close to, a pad, or be covered up by the component once it is assembled. However, at the level of the footprint library, it makes sense to have the initial location of the reference text in the centre of the footprint, to make things easier when we are moving them around to their final locations in the PCB layout, before laying tracks and moving the text items to their final locations.

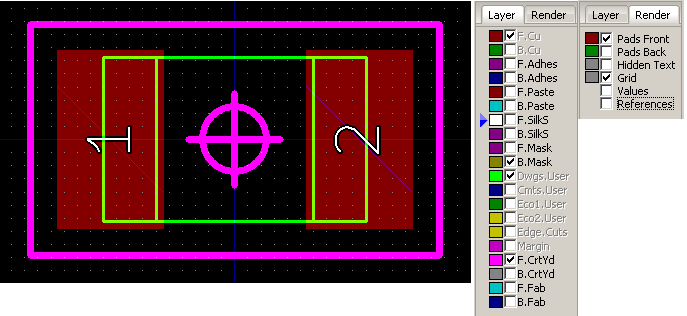

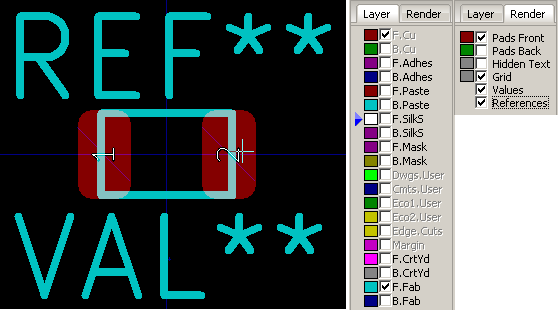

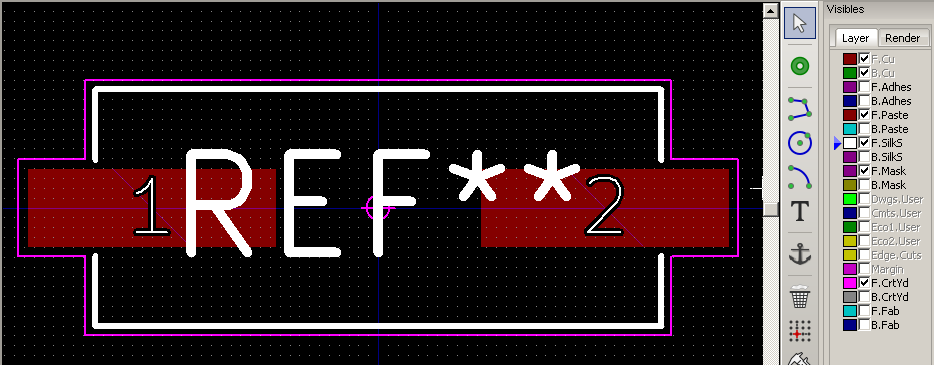

In both Pcbnew and Footprint Editor (this is with a Windows nightly from 2017-09-19) I changed some layer colours:

F.SilkS White

Dwgs.User Green 4

F.CrtYd Magenta 4

F.Fab Cyan 3

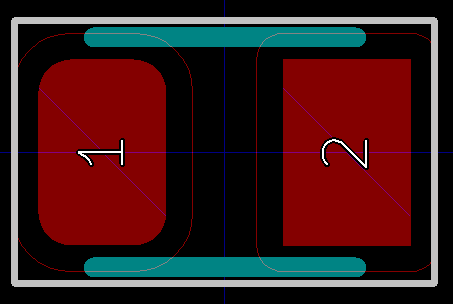

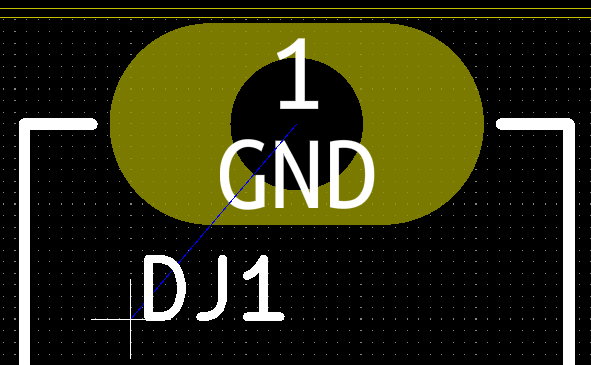

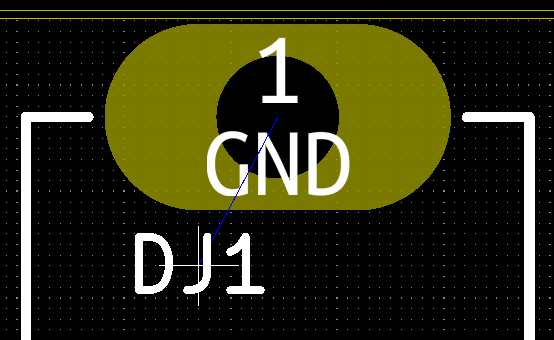

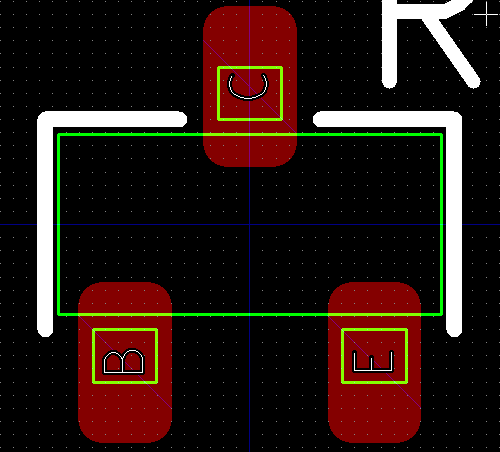

Once imported into Footprint Editor, this footprint's initial appearance is:

Here is the F.cu , F.CrtYd and Dwgs.User , with Hidden Text, Values and References not displayed:

The resistor outline and terminal rectangles are superimposed on the Dwgs.User layer, but they are all separate lines so I could alter them if I wished, such as to show only the component outline. Alternatively I could have set Library Expert Lite to show only the outline and not the terminals by altering some settings in the Drafting tab > Assembly sub-tab from what I used, by default:

Next, we see just the pads and the silkscreen, with Values and References displayed.

I edited the pads to be rounded rectangles, by right clicking pad 1 and selecting Rounded Rectangle, and then by right clicking pad 2 and selecting Apply Pad Settings, which requires no further action to make the same change to the second pad. I turned off the F.Silk layer and turned on F.Fab and moved the REF** text up and the VAL** text down, to reduce clutter. However, this would not be a change I make to the footprint - best to keep them in the central location to simplify moving the instances of footprints around the PCB design in the early stages of the design. Also, it is possible to turn on and off the display of References and Values, in Footprint Editor and in Pcbnew, which means they can be in the centre of the component and not clutter each other up if we use these display options selectively:

#roundedrectangles

Here is the text of the footprint, as exported from Footprint Editor, after a single change: selecting rounded rectangle pads. The order but not the content of the first and third fp_text items has been reversed by this process. The only other changes are in red: a timestamp and the extra text for rounded rectangles:

So far, so good. I have created an apparently IPC-7351C-compliant

footprint, based on looking up a manufacturer's datasheet to get the

physical dimensions of the component, and I have exported it into KiCad

and changed the pads to rounded rectangles.

But is this really what I want? How would I know? I haven't yet designed a proper PCB with KiCad, much less had the boards made and automatically assembled.

So I contemplated this simple footprint in the light of what I could glean from far more experienced people who wrote in thread00. They were writing in mid-2016, when KiCad's capabilities were perhaps somewhat different.

For me, the most significant material in this thread was written by Mars_Warrior, including these two messages: https://forum.kicad.info/t/why-are-the-kicad-library-conventions-non-ipc-compliant/3678/12 and https://forum.kicad.info/t/why-are-the-kicad-library-conventions-non-ipc-compliant/3678/62 .

"fabhouse" means the company which does automated SMT assembly. (I use the term "PCB fabricator" to refer to the company which makes the bare printed circuit boards.) "refdes" means the reference, or reference designator, for instance U4, C37 etc.

Here is a cheatsheet correlating the default colours of Library Expert's layers, with their mouseover texts and the default layers they correspond to when the footprint is converted to a KiCad file. The full resolution version is: library-expert-layer-colours.png .

The last item NUM does not seem to be a layer, but enables the display of the pad numbers over the top of everything else. Right-clicking the colour box enables us to change the colour - except that some items such as ADTL do not have a colour, since this is set by the ADT item.

Three extra items appear (at least sometimes, for me) below item NUM:

- GRID Right click to set the X and Y dimensions, but I don't see any grid.

- BG Background colour.

- HLT

Highlight colour. The cursor, together with potentially the

control key can be used to select one or more things, but I could only

get it to work with pads at first, until I discovered that by right

clicking in an empty area of the display window, I can select which of Pins, Shapes, Lines and Labels are available for selection. Once an item is selected, right-click

brings up a properties box.

Here are some examples of the display with only particular layers turned on:

This shows the pads represented by Top copper (F.Cu) in blue, with pin numbers and the TRM layer showing the terminals. The magenta is Top Courtyard, which is converted to KiCad's F.CrtYd layer. The circle (target) and crosshairs can be turned off and resized in the various tab and sub-tabs mentioned above. The little white thing in the middle is not part of the footprint - this is Library Expert showing where 0,0 is.

I turned off the terminals and turned on the Body Outline. Both these layers are converted to KiCad's Dwgs.User layer.

I understand the the Courtyard layer (there are front and back ones in KiCad) is used when laying out the PCB so that each component is kept a suitable distance from the other. I guess it may also be useful, with these crosshairs and targets, for the assembly company, but they should in principle be able to see where each component's centre is via the .POS file.

On top, because it was the most recent layer I turned on, is the Assembly Drawing Top's rectangle showing the outline of the resistor. The Assembly Drawing Top Label is depicted as well as Name, but all that matters to us is its orientation and position. This represents where two items will be in the converted footprint, both on the F.Fab layer, which is where the four lines of the rectangle will be as well: text value containing VAL** and text reference containing REF**. (See below for details of how KiCad interprets these fp_text items. From the exported footprint itself:

(fp_text user %R (at 0 0) (layer F.SilkS)

(effects (font (size 0.77 0.77) (thickness 0.08)))

)

(fp_text value VAL** (at 0 0) (layer F.Fab)

(effects (font (size 1.2 1.2) (thickness 0.12)))

)

(fp_text reference REF** (at 0 0) (layer F.Fab)

(effects (font (size 1.2 1.2) (thickness 0.12)))

)

(effects (font (size 0.77 0.77) (thickness 0.08)))

)

(fp_text value VAL** (at 0 0) (layer F.Fab)

(effects (font (size 1.2 1.2) (thickness 0.12)))

)

(fp_text reference REF** (at 0 0) (layer F.Fab)

(effects (font (size 1.2 1.2) (thickness 0.12)))

)

I was puzzled as to why the first item of text in the excerpt above is made so small: 0.77mm high. This is probably due to the fact that the whole component is small and the range of text sizes which are, by default in this program (presumably matching the specifications of the soon-to-be released IPC-7351C standard) set to 0.50mm to 2.00mm. This is in the Drafting tab > Assembly sub-tab:

Since my PCB fabricator http://www.pcbfast.com.au/techinfo/silkscreen-legends/ specifies for the silkscreen:

Inkjet Liquid Photo Imaging (More expensive.)

Min text height 0.80mm 0.50mm

Min line width 0.15mm 0.10mm

Min text height 0.80mm 0.50mm

Min line width 0.15mm 0.10mm

which preclude this part of the converted footprint from being used as is:

(effects (font (size 0.77 0.77) (thickness 0.08)))

So the solution will be to alter these settings before creating components. This needs to be done for each component, as far as I know, with Library Expert Lite, but can be set in preference file for the Pro version.

#seeestudiodfm

Also, the widely-cited SeeedStudio document: http://www.seeedstudio.com/blog/2017/06/08/free-pcb-dfm-manual-v1-1-available-in-seeed-fusion/ states (page 7) that the silkscreen's minimum character height is 0.6mm and line width 0.1mm.

Once the footprint is placed in the PCB design, we can change these things manually, but it would probably be best to get the footprint in the library set so its default state doesn't violate the restrictions on what we can have made. These changes can be made in Footprint Editor, but it might be better to tweak Library Expert Lite to set the values within proper limits. (Later I decided to set the size of these text items on all layers to 0.8mm in a later edit of the footprint file, before importing it into Footprint Editor for review and saving to my library.)

There are three separate layers in this Library Expert system (for the top = front side) which correspond to the pad:

PMT Paste Mask Top

SMT Solder Mask Top

TOP Top (copper)

SMT Solder Mask Top

TOP Top (copper)

however they all show the same thing, in this example, and at least for this particular footprint, all three aspects of the pad are defined in a single line for each pad, all with the same size:

(pad 1 smd rect (at -0.95 0) (size 0.81 1.36) (layers F.Cu F.Paste F.Mask))

(pad 2 smd rect (at 0.95 0) (size 0.81 1.36) (layers F.Cu F.Paste F.Mask))

(pad 2 smd rect (at 0.95 0) (size 0.81 1.36) (layers F.Cu F.Paste F.Mask))

Here is the image which results from the final combination of layers turned on:

The two lines are the silkscreen indication of the location of the resistor. Other footprints have more elaborate arrangements, including the presence or absence of a line within this shape to indicate polarity (the location of pin 1, or the positive terminal etc.) - or alternatively the presence of a dot to indicate this. IPC-7351C specifies that no part of the silkscreen image should be in the same place, or close to, a pad, or be covered up by the component once it is assembled. However, at the level of the footprint library, it makes sense to have the initial location of the reference text in the centre of the footprint, to make things easier when we are moving them around to their final locations in the PCB layout, before laying tracks and moving the text items to their final locations.

In both Pcbnew and Footprint Editor (this is with a Windows nightly from 2017-09-19) I changed some layer colours:

F.SilkS White

Dwgs.User Green 4

F.CrtYd Magenta 4

F.Fab Cyan 3

Once imported into Footprint Editor, this footprint's initial appearance is:

Here is the F.cu , F.CrtYd and Dwgs.User , with Hidden Text, Values and References not displayed:

The resistor outline and terminal rectangles are superimposed on the Dwgs.User layer, but they are all separate lines so I could alter them if I wished, such as to show only the component outline. Alternatively I could have set Library Expert Lite to show only the outline and not the terminals by altering some settings in the Drafting tab > Assembly sub-tab from what I used, by default:

Next, we see just the pads and the silkscreen, with Values and References displayed.

I edited the pads to be rounded rectangles, by right clicking pad 1 and selecting Rounded Rectangle, and then by right clicking pad 2 and selecting Apply Pad Settings, which requires no further action to make the same change to the second pad. I turned off the F.Silk layer and turned on F.Fab and moved the REF** text up and the VAL** text down, to reduce clutter. However, this would not be a change I make to the footprint - best to keep them in the central location to simplify moving the instances of footprints around the PCB design in the early stages of the design. Also, it is possible to turn on and off the display of References and Values, in Footprint Editor and in Pcbnew, which means they can be in the centre of the component and not clutter each other up if we use these display options selectively:

#roundedrectangles

Here is the text of the footprint, as exported from Footprint Editor, after a single change: selecting rounded rectangle pads. The order but not the content of the first and third fp_text items has been reversed by this process. The only other changes are in red: a timestamp and the extra text for rounded rectangles:

(module RESC200X125X60L40N (layer F.Cu) (tedit 59EB4182) (descr "Resistor, Chip; 2.00 mm L X 1.25 mm W X 0.60 mm H body") (attr smd) (fp_text reference REF** (at 0 0) (layer F.Fab) (effects (font (size 1.2 1.2) (thickness 0.12))) )

(fp_text value VAL** (at 0 0) (layer F.Fab)

(effects (font (size 1.2 1.2) (thickness 0.12)))

)

(fp_text user %R (at 0 0) (layer F.SilkS)

(effects (font (size 0.77 0.77) (thickness 0.08)))

)

(fp_line (start -0.6 -0.625) (end -0.6 0.625) (layer Dwgs.User) (width 0.025))

(fp_line (start -0.6 0.625) (end -1 0.625) (layer Dwgs.User) (width 0.025))

(fp_line (start -1 0.625) (end -1 -0.625) (layer Dwgs.User) (width 0.025))

(fp_line (start -1 -0.625) (end -0.6 -0.625) (layer Dwgs.User) (width 0.025))

(fp_line (start 0.6 0.625) (end 0.6 -0.625) (layer Dwgs.User) (width 0.025))